## OMAP5910 Dual-Core Processor MPU Subsystems Reference Guide

Literature Number: SPRU671 October 2003

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated

### Preface

## **Read This First**

#### About This Manual

This document describes the core, caches, memory management units (MMUs), interface, and bridges of the OMAP5910 multimedia processor microprocessor unit (MPU) subsystem.

#### **Notational Conventions**

This document uses the following conventions.

□ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

#### **Related Documentation From Texas Instruments**

The following documents describe the OMAP5910 device and related peripherals. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

*OMAP5910 Dual-Core Processor MPU Subsystem Reference Guide* (literature number SPRU671)

*OMAP5910 Dual-Core Processor DSP Subsystem Reference Guide* (literature number SPRU672)

*OMAP5910 Dual-Core Processor Memory Interface Traffic Controller Reference Guide* (literature number SPRU673)

*OMAP5910 Dual-Core Processor System DMA Controller Reference Guide* (literature number SPRU674)

*OMAP5910 Dual-Core Processor LCD Controller Reference Guide* (literature number SPRU675)

OMAP5910 Dual-Core Processor Universal Asynchronous Receiver/Transmitter (UART) Devices Reference Guide (literature number SPRU676)

5

OMAP5910 Dual-Core Processor Universal Serial Bus (USB) and Frame Adjustment Counter (FAC) Reference Guide (literature number SPRU677)

OMAP5910 Dual-Core Processor Clock Generation and System Reset Management Reference Guide (literature number SPRU678)

OMAP5910 Dual-Core Processor General-Purpose Input/Output (GPIO) Reference Guide (literature number SPRU679)

*OMAP5910 Dual-Core Processor MMC/SD Reference Guide* (literature number SPRU680)

*OMAP5910 Dual-Core Processor Inter-Integrated Circuit (I2C) Controller Reference Guide* (literature number SPRU681)

*OMAP5910 Dual-Core Processor Timer Reference Guide* (literature number SPRU682)

*OMAP5910 Dual-Core Processor Inter-Processor Communication Reference Guide* (literature number SPRU683)

*OMAP5910 Dual-Core Processor Camera Interface Reference Guide* (literature number SPRU684)

*OMAP5905 Dual-Core Processor Multichannel Serial Interface (MCSI) Reference Guide* (literature number SPRU685)

**OMAP5910 Dual-Core Processor Micro-Wire Interface Reference Guide** (literature number SPRU686)

*OMAP5910 Dual-Core Processor Real-Time Clock (RTC) Reference Guide* (literature number SPRU687)

OMAP5910 Dual-Core Processor HDQ/1-Wire Interface Reference Guide (literature number SPRU688)

*OMAP5910 Dual-Core Processor PWL, PWT, and LED Peripheral Reference Guide* (literature number SPRU689)

*OMAP5910 Dual-Core Processor Multichannel Buffered Serial Port (McBSP) Reference Guide* (literature number SPRU708)

#### Trademarks

6

OMAP and the OMAP symbol are trademarks of Texas Instruments.

## Contents

| 1 | Introd                                          | luction                                                                                                                                                                                                                                                        | 1                          |

|---|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2 | MPU                                             | Core                                                                                                                                                                                                                                                           | 2                          |

| 3 | <b>Instru</b><br>3.1<br>3.2                     | <b>uction Cache</b>                                                                                                                                                                                                                                            | 3                          |

| 4 | <b>Data</b><br>4.1<br>4.2<br>4.3                | Cache14D-Cache Operation14Validity15Double-Mapped Space16                                                                                                                                                                                                      | 4<br>5                     |

| 5 | <b>Write</b><br>5.1<br>5.2                      | Buffer       16         Operation       17         SWAP Instruction       17                                                                                                                                                                                   | 7                          |

| 6 | <b>Copro</b><br>6.1<br>6.2                      | CP15 Access18Register Descriptions186.2.1 ID Register and Cache Information Register186.2.2 Cache Operations276.2.3 TLB Operations286.2.4 TLB Lock-Down Registers296.2.5 Context Switch (or PID: Process Identifier) Register376.2.6 TI Operations37           | 8<br>9<br>7<br>9           |

| 7 | MPU 1<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6 | Memory Management Unit34Translation Look-Aside Buffer34Translation Table35Domains and Access Permissions35MMU Program-Accessible Registers36Address Translation36Translation Process377.6.1Translation Table Base7.6.2Level-1 Fetch36367.6.3Level-1 Descriptor | 4<br>5<br>6<br>7<br>8<br>8 |

|    |              | 7.6.4 Translating Section References                                                                      |    |

|----|--------------|-----------------------------------------------------------------------------------------------------------|----|

|    |              | 7.6.5 Level-2 Descriptor                                                                                  |    |

|    |              | <ul><li>7.6.6 Translating Tiny Pages References</li><li>7.6.7 Translating Small Page References</li></ul> |    |

|    |              | 7.6.8 Translating Large Page References                                                                   |    |

|    | 7.7          | MMU Faults and MPU Aborts                                                                                 |    |

|    | 7.8          | Fault Address and Fault Status Registers (FAR and FSR)                                                    |    |

|    | 7.9          | Domain Access Control                                                                                     |    |

|    | 7.10         | Permission Access                                                                                         |    |

|    | 7.11         | Fault Checking Sequence                                                                                   |    |

|    |              | 7.11.1 Alignment Fault                                                                                    |    |

|    |              | 7.11.2Translation Fault7.11.3Domain Fault                                                                 |    |

|    |              | 7.11.4 Permission Fault                                                                                   |    |

|    | 7.12         | External Aborts                                                                                           |    |

|    | 7.13         | Buffered Writes                                                                                           |    |

| •  |              | Memory Management Unit                                                                                    |    |

| 8  |              |                                                                                                           |    |

| 9  |              |                                                                                                           |    |

|    | 9.1          | Functional Features                                                                                       |    |

|    | 9.2          | MPUI Registers                                                                                            | 65 |

| 10 | MPU          | TI Peripheral Bus Bridges                                                                                 |    |

|    | 10.1         | 8-Bit, 16-Bit, and 32-Bit Word Access                                                                     |    |

|    | 10.2         | TIPB Allocation                                                                                           |    |

|    | 10.3<br>10.4 | Access Factor and Time-Out                                                                                |    |

|    | 10.4         | MPU Posted Write Pipeline Mode                                                                            |    |

|    | 10.5         | Abort                                                                                                     |    |

|    | 10.7         | TIPB Bridge Registers                                                                                     |    |

| 44 | MDU          | Interrupt Handlers                                                                                        |    |

|    | 11.1         | MPU Level-1 Interrupt Handler                                                                             |    |

|    | 11.2         | MPU Level 2 Interrupt Handler                                                                             |    |

| 10 |              | -1 and Level-2 Interrupt Mapping                                                                          |    |

|    |              |                                                                                                           |    |

|    |              | upt Handler Level-1 and Level-2 Registers                                                                 |    |

| 14 |              | guration Module                                                                                           |    |

|    | 14.1         | Configuration Register Capabilities                                                                       |    |

|    | 14.2<br>14.3 | OMAP5910 Native and Compatibility ModesOMAP5910 Generic Pin Multiplexing and Pullup/Pulldown Control      |    |

|    | 14.3         | OMAP5910 Generic Phr Multiplexing and Pullup/Pullowin Control                                             |    |

| 15 |              | P5910 Configuration Registers                                                                             |    |

|    |              | e Identification                                                                                          |    |

| 10 | 16.1         | Identification Code Register                                                                              |    |

|    | 16.2         | Die Identification (ID)                                                                                   |    |

|    | 10.2         |                                                                                                           |    |

| 17 | MPU Private Peripherals Overview                                                                                                                                | . 135                   |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 18 | MPU Public Peripherals Overview                                                                                                                                 | . 136                   |

| 19 | MPU/DSP Peripherals Overview                                                                                                                                    | . 137                   |

| 20 | Endianism Conversion         20.1       Conversion Through the DSP MMU         20.2       Conversion Through the MPUI                                           | . 139                   |

|    | ETM Environment         21.1       ETM Features         21.2       ETM Interface         21.3       Operation         21.4       Additional Reference Materials | . 143<br>. 143<br>. 144 |

# Figures

|    |                                                     | _  |

|----|-----------------------------------------------------|----|

| 1  | Highlight of MPU Subsystem                          |    |

| 2  | MRC, MCR Bit Pattern 1                              |    |

| 3  | Format of the CP15 Translation Table Base Register  |    |

| 4  | Format of the CP15 Domain Access Control Register 2 |    |

| 5  | Format of the Fault Address Register 2              |    |

| 6  | D-Cache Clean/Flush Single Entry Operand Format 2   |    |

| 7  | Format of the Lock-Down Registers 3                 |    |

| 8  | Format of the I_min and I_max Registers 3           | 3  |

| 9  | Format of the Thread-ID Register 3                  | 3  |

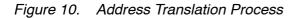

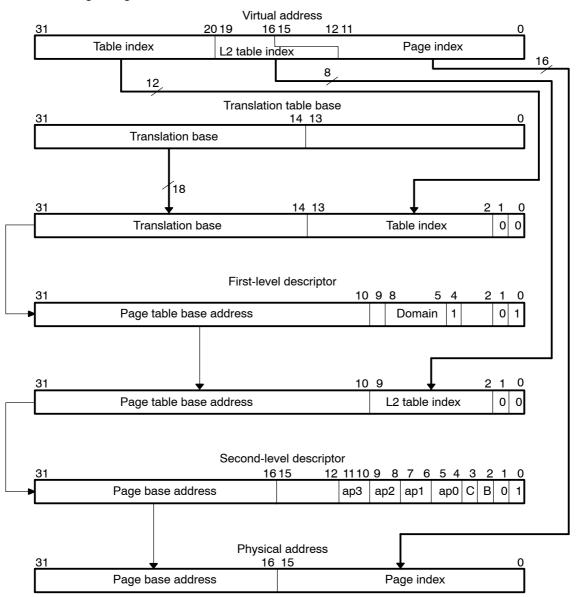

| 10 | Address Translation Process                         | 57 |

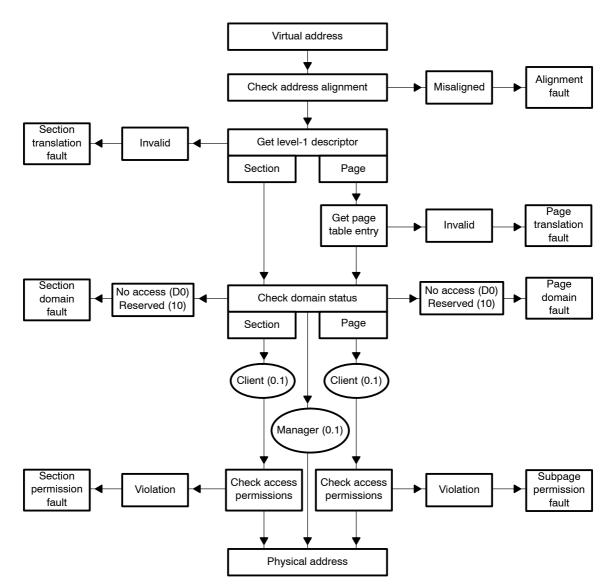

| 11 | Translation Table Base Register 3                   | 8  |

| 12 | Accessing the Translation Table Level-1 Descriptors | 9  |

| 13 | Level-1 Descriptors                                 | 9  |

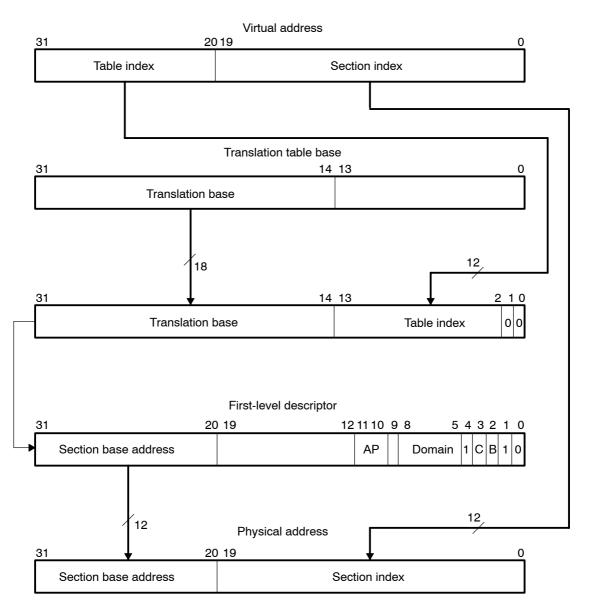

| 14 | Section Translation 4                               | 2  |

| 15 | Page Table Entry (Level-2 Descriptor) 4             | -3 |

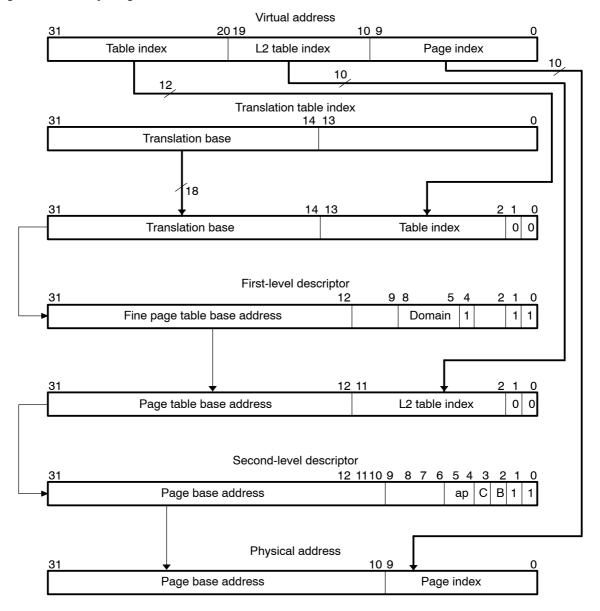

| 16 | Tiny Page Translation                               | -5 |

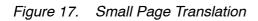

| 17 | Small Page Translation 4                            | 6  |

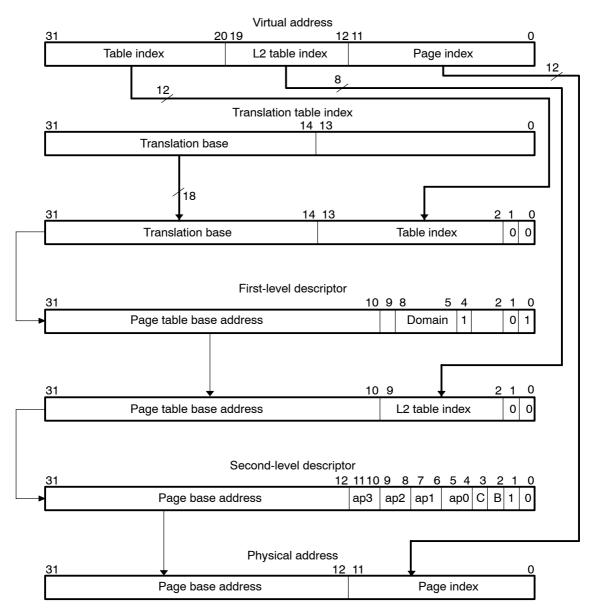

| 18 | Large Page Translation 4                            | 8  |

| 19 | Domain Access Control Register Format 5             | 0  |

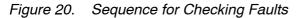

| 20 | Sequence for Checking Faults 5                      | 52 |

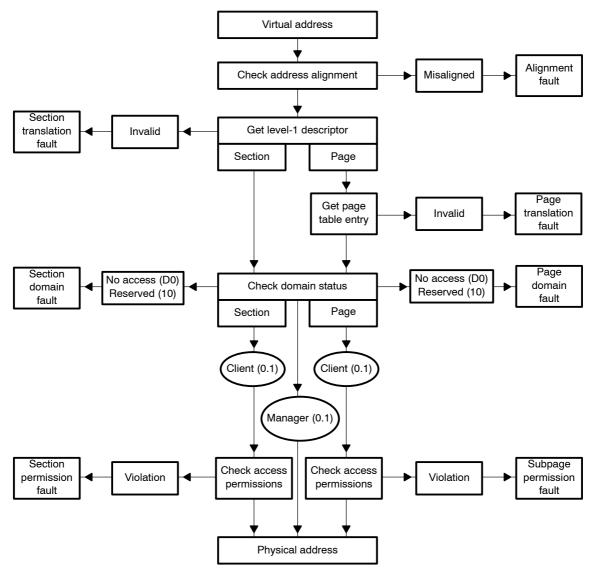

| 21 | Nonaligned Read-Word Access                         | 53 |

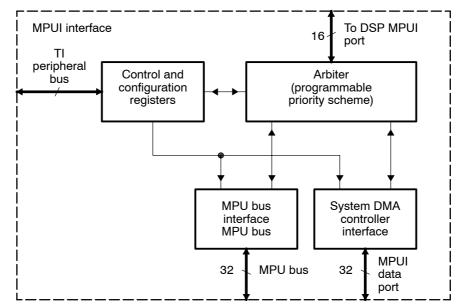

| 22 | MPUI Simplified Block Diagram                       | 63 |

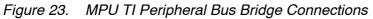

| 23 | MPU TI Peripheral Bus Bridge Connections            | '3 |

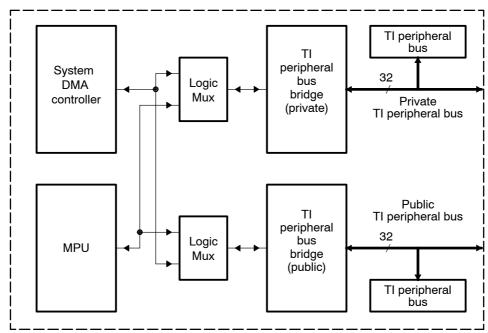

| 24 | MPU Interrupt Handlers                              | '9 |

| 25 | MPU Private Peripherals                             |    |

| 26 | MPU Public Peripherals Area                         | 57 |

| 27 | Highlight of MPU/DSP Peripherals                    |    |

| 28 | DSP Endian Conversion, 32-Bit Aligned Data          |    |

| 29 | DSP Endian Conversion, MPUI Port Boundary           |    |

| 30 | Required System for ETM Usage                       |    |

## **Tables**

| 1  | Data Cache Configuration                                               | 14 |

|----|------------------------------------------------------------------------|----|

| 2  | Write Buffer Configuration                                             | 17 |

| 3  | CP15 Register Summary                                                  | 19 |

| 4  | Reading From CP15 Register 0                                           | 20 |

| 5  | CP15 ID Register                                                       |    |

| 6  | CP15 Cache Information Register (CIR)                                  | 20 |

| 7  | CP15 Control Register                                                  | 22 |

| 8  | Domain Configuration                                                   | 26 |

| 9  | CP15 Fault Status Register                                             | 26 |

| 10 | Cache Operations                                                       | 27 |

| 11 | TLB Operations                                                         | 29 |

| 12 | Lockdown Operations                                                    | 30 |

| 13 | TI Operations                                                          | 31 |

| 14 | TI925T Configuration Register                                          | 31 |

| 15 | TI925T_status Register                                                 | 33 |

| 16 | CP15 Registers or Functions Used by the MMU                            | 36 |

| 17 | Level-1 Fine Page Table Descriptor                                     | 40 |

| 18 | Interpreting Level-1 Descriptor Bits 1–0                               | 40 |

| 19 | Level-1 Coarse Page Table Descriptor                                   | 41 |

| 20 | Level-1 Section Descriptor                                             | 41 |

| 21 | Level-2 Section Descriptor                                             | 43 |

| 22 | Interpreting Page Table Entry Bits 1–0                                 | 44 |

| 23 | Priority Encoding of the Fault Status Register                         | 49 |

| 24 | Interpreting Access Bits in Domain Access Control Register             | 50 |

| 25 | Interpreting Access Permission                                         | 50 |

| 26 | DSP Memory Management Unit Registers                                   | 55 |

| 27 | Prefetch Register (PREFETCH_REG)) – Offset Address (hex): 00           | 56 |

| 28 | Prefetch Status Register (WALKING_ST_REG) – Offset Address (hex): 04   | 57 |

| 29 | Control Register (CNTL_REG) – Offset Address (hex): 08                 | 57 |

| 30 | Fault Address Register MSB (FAULT_AD_H_REG) – Offset Address (hex): 0C | 57 |

| 31 | Fault Address Register LSB (FAULT_AD_L_REG) – Offset Address (hex): 10 | 58 |

| 32 | Fault Status Register (F_ST_REG)) – Offset Address (hex): 14           | 58 |

| 33 | IT Acknowledge Register (IT_ACK_REG) – Offset Address (hex): 18        | 58 |

| 34 | TTB Register MSB (TTB_H_REG) – Offset Address (hex): 1C                | 58 |

| 35 | TTB Register LSB (TTB_L_REG) – Offset Address (hex): 20                |    |

| 36 | Lock Counter Register (LOCK_REG) – Offset Address (hex): 24            | 59 |

| 37 | Load Entry in TLB Register (LD_TLB_REG) – Offset Address (hex): 28    | 59 |

|----|-----------------------------------------------------------------------|----|

| 38 | CAM Entry Register MSB (CAM_H_REG) – Offset Address (hex): 2C         | 59 |

| 39 | CAM Entry Register LSB (CAM L REG) – Offset Address (hex): 30         | 60 |

| 40 | RAM Entry Register MSB (RAM_H_REG) – Offset Address (hex): 34         | 60 |

| 41 | RAM Entry Register LSB (RAM L REG) – Offset Address (hex): 38         |    |

| 42 | Global Flush Register (GFLUSH REG) – Offset Address (hex): 3C         | 61 |

| 43 | Individual Flush Register (FLUSH_ENTRY_REG) – Offset Address (hex):40 | 61 |

| 44 | CAM Entry Register MSB (READ_CAM_H_REG) – Offset Address (hex): 44    | 61 |

| 45 | CAM Entry Register LSB (CAM CAM L REG) - Offset Address (hex): 48     | 61 |

| 46 | RAM Entry Register MSB (READ_RAM_H_REG) – Offset Address (hex): 4C    | 62 |

| 47 | RAM Entry Register LSB (READ_RAM_L_REG) – Offset Address (hex): 50    | 62 |

| 48 | MPUI Registers                                                        | 65 |

| 49 | Control Register (CTRL_REG) – Offset: x00                             | 66 |

| 50 | Debug Address Register (DEBUG_ADDR) – Offset: x04                     | 67 |

| 51 | Debug Data Register (DEBUG_DATA) – Offset: x08                        | 68 |

| 52 | Debug Flag Register (DEBUG_FLAG) – Offset: x0C                        | 68 |

| 53 | Status Register (STATUS_REG) – Offset: x10                            | 69 |

| 54 | DSP Status Register (DSP_STATUS_REG) – Offset: x14                    | 70 |

| 55 | DSP Boot Configuration Register (DSP_BOOT_CONFIG) – Offset: x18       | 71 |

| 56 | DSP MPUI Configuration Register (DSP_API_CONFIG) – Offset: x1C        | 72 |

| 57 | Decoding SARAM 0 Through SARAM 11 on 8K Boundaries                    | 72 |

| 58 | Access Factor                                                         | 74 |

| 59 | TIPB (Private) Bridge Registers                                       | 75 |

| 60 | TIPB (Public) Bridge Registers                                        |    |

| 61 | TIPB Control Register (TIPB_CNTL) – Offset: x00                       | 76 |

| 62 | TIPB Bus Allocation Register (TIPB_BUS_ALLOC) – Offset: x04           | 76 |

| 63 | MPU TIPB Control Register (MPU_TIPB_CNTL_REG) – Offset: x08           | 77 |

| 64 | Enhanced TIPB Control Register (ENHANCED_TIPB_CNTL) – Offset: x0C     |    |

| 65 | Address Debug Register (ADDRESS_DBG) – Offset: x10                    | 77 |

| 66 | Data Debug Register LSB (DATA_DEBUG_LOW) – Offset: x14                |    |

| 67 | Data Debug Register MSB (DATA_DEBUG_HIGH) – Offset: x18               | 77 |

| 68 | Debug Control Signals Register (DEBUG_CNTR_SIG) – Offset: x1C         |    |

| 69 | Level-1 and Level-2 OMAP5910 MPU Interrupt Mapping                    |    |

| 70 | Interrupt Handler Registers                                           |    |

| 71 | Interrupt Input Register (ITR)                                        |    |

| 72 | Mask Interrupt Register (MIR)                                         |    |

| 73 | Binary-Coded Source IRQ Register (SIR_IRQ_CODE)                       |    |

| 74 | Binary-Coded Source FIQ Register (SIR_FIQ_CODE)                       |    |

| 75 | Control Register (CONTROL_REG)                                        |    |

| 76 | Interrupt Level Registers (ILR0ILR31)                                 |    |

| 77 | Interrupt Set Register (ISR)                                          | 88 |

| 78 | Functional Pin Multiplexing Control Register 3                        |    |

|    | (FUNC_MUX_CTRL3FUNC_MUX_CTRLD)                                        |    |

| 79 | Configuration Registers                                               | 91 |

| 80  | Functional Multiplexing Control 0 Register (FUNC MUX CTRL 0) |

|-----|--------------------------------------------------------------|

| 81  | Functional Multiplexing Control 1 Register (FUNC_MUX_CTRL_1) |

| 82  | Functional Multiplexing Control 2 Register (FUNC MUX CTRL 2) |

| 83  | Compatibility Mode Control 0 Register (COMP_MODE_CTRL_0)     |

| 84  | Functional Multiplexing Control 3 Register (FUNC MUX CTRL 3) |

| 85  | Functional Multiplexing Control 4 Register (FUNC_MUX_CTRL_4) |

| 86  | Functional Multiplexing Control 5 Register (FUNC MUX CTRL 5) |

| 87  | Functional Multiplexing Control 6 Register (FUNC MUX CTRL 6) |

| 88  | Functional Multiplexing Control 7 Register (FUNC MUX CTRL 7) |

| 89  | Functional Multiplexing Control 8 Register (FUNC_MUX_CTRL_8) |

| 90  | Functional Multiplexing Control 9 Register (FUNC MUX CTRL 9) |

| 91  | Functional Multiplexing Control A Register (FUNC MUX CTRL A) |

| 92  | Functional Multiplexing Control B Register (FUNC MUX CTRL B) |

| 93  | Functional Multiplexing Control C Register (FUNC MUX CTRL C) |

| 94  | Functional Multiplexing Control D Register (FUNC_MUX_CTRL_D) |

| 95  | Pulldown Control 0 Register (PULL DWN CTRL 0)                |

| 96  | Pulldown Control 1 Register (PULL DWN CTRL 1)                |

| 97  | Pulldown Control 2 Register (PULL DWN CTRL 2)                |

| 98  | Pulldown Control 3 Register (PULL DWN CTRL 3)                |

| 99  | Gate and Inhibit Control 0 Register (GATE_INH_CTRL_0)        |

| 100 | Voltage Control 0 Register (VOLTAGE CTRL 0)                  |

| 101 | Test Debug Control 0 Register (TEST_DBG_CTRL_0)              |

| 102 | Module Configuration Control 0 Register (MOD_CONF_CTRL_0)    |

| 103 | ID Code Register (IDCODE)                                    |

| 104 | ID Code Register (IDCODE) Bits                               |

| 105 | Die ID Address Space—Private TIPB Bridge 135                 |

| 106 | Little-Endian Data Format                                    |

| 107 | Big-Endian Format                                            |

| 108 | DSP Data Format                                              |

|     |                                                              |

This document describes the core, caches, memory management units (MMUs), interface, and bridges of the OMAP5910 multimedia processor microprocessor unit (MPU) subsystem.

#### 1 Introduction

The MPU of the OMAP5910 device controls the memory management units (MMUs), the system direct memory access (DMA) controller, the MPU TI peripheral bus (TIPB) bridge, and peripherals.

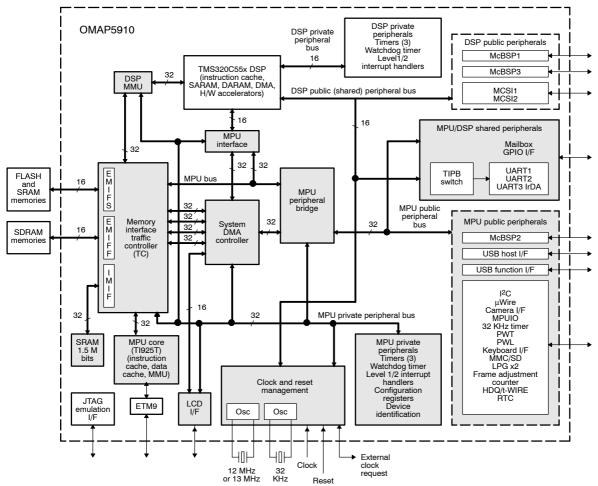

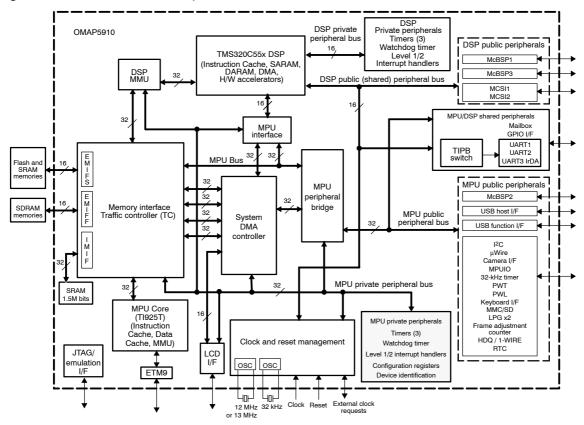

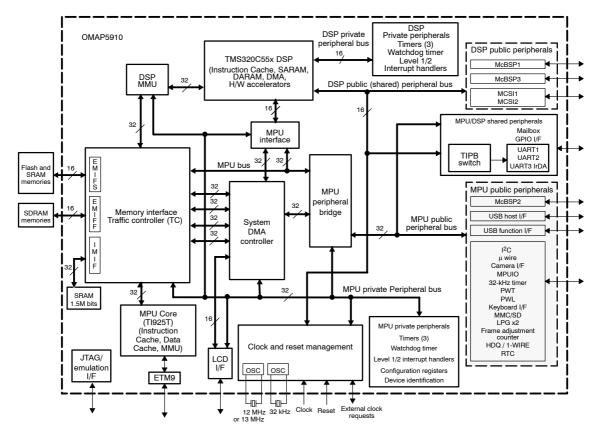

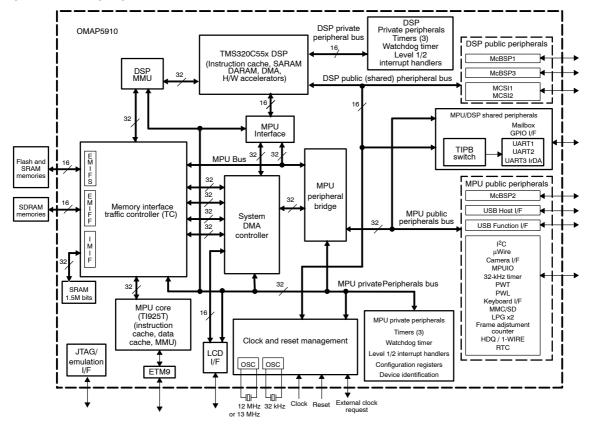

Figure 1 shows the OMAP5910 device with the MPU subsystem highlighted. The subsystem contains the following components:

- MPU core (see Section 2, MPU Core)

- □ Traffic controller (see SPRU673, *Memory Interface Traffic Controller Reference Guide*)

- MPU MMU (see Section 7, MPU Memory Management Unit)

- DSP MMU (see Section 8, DSP Memory Management Unit)

- System DMA controller (see SPRU674 , System DMA Controller Reference Guide)

- LCD controller (see SPRU675, *LCD Controller Reference Guide*)

- MPU TIPB bridge (see Section 10, MPU TI Peripheral Bus Bridges)

- Clock manager (see SPRU678, *Clock Generation and System Reset Management Reference Guide*)

- □ Interrupt handler (see Section 1. 11, MPU Interrupt Handler)

- Timers (see SPRU682, Timer Reference Guide)

- U Watchdog timer (see SPRU682, Tmer Reference Guide)

- Interprocessor communication (see SPRU683, Interprocessor Communication Reference Guide)

- 1.5M-bit SRAM internal memory

Figure 1. Highlight of MPU Subsystem

#### 2 MPU Core

The MPU core is a TI925T reduced instruction set computer (RISC) processor. The TI925T is a 32-bit processor core that performs 32-bit or 16-bit instructions and processes 32-bit, 16-bit, or 8-bit data. The core uses pipelining so that all parts of the processor and memory system can operate continuously.

The MPU core incorporates:

- A co-processor 15 (CP15) and protection module

- Data and program memory management units (MMUs) with table look-aside buffers.

- □ A separate 16K-byte instruction cache and 8K-byte data cache. Both are two-way associative with virtual index virtual tag (VIVT).

- □ A 17-word write buffer (WB)

- A local bus interface

The OMAP5910 device uses the TI925T core in little-endian mode only.

To reduce effective memory access time, the TI925T has an instruction cache, a data cache, and a write buffer. In general, these are transparent to program execution.

#### 3 Instruction Cache

The 16K-byte instruction cache (I-cache) has 1024 lines of 16 bytes arranged as a two-way set-associative cache. It uses the virtual addresses generated by the processor core. The I-cache is always reloaded one line at a time. It can be enabled or disabled via the CP15 control register (I\_CP15 bit) and is disabled and flushed upon reset.

Disabling the I-cache does not invalidate it.

The I-cache can be independently enabled from the MMU.

#### 3.1 Operation

When the I-cache is enabled, it is searched whenever the processor requests an instruction. If the cache hits, data is returned to the core whether the MMU is enabled or not. If a cache read misses, a line fetch is performed and data is written to the cache following a least recently used (LRU) replacement algorithm. For best performance, enable the I-cache as soon as possible after reset. If the I-cache is disabled, it is not searched. All instruction fetches generate a single 16-bit or 32-bit external access. An instruction miss generates line load. The LOAD\_MULTIPLE instruction does not perform a burst read.

#### 3.2 Validity

The flush I-cache instruction is fetched at cycle time 0, for example, but not executed until cycle time 4 (the TI925T uses a five-stage opcode pipe). Thus, four additional opcodes may be fetched from the I-cache before the flush I-cache opcode is executed. Once executed, the entire I-cache is invalidated before the next opcode executes. Typically, four non-opcodes following the CP15 instruction flush the cache to avoid confusion.

The I-cache content is not flushed when the I-cache is disabled. Its contents remain valid and are accessible again when the I-cache is reenabled.

#### 4 Data Cache

The 8K byte data cache (D-cache) has 512 lines of 16 bytes arranged as a two-way set-associative cache. It uses the virtual addresses generated by the processor. The D-cache is always reloaded one line at a time, because it always requires the MMU to be enabled. The D-cache is always disabled when the MMU is off. The MMU can operate in write-through (WT) or in copy-back (CB) mode. The translation lookaside buffer (TLB) descriptors that are placed in memory determine which mode is used.

The D-cache can be enabled or disabled via the CP15 control register: the D-cache is disabled and flushed upon reset. The D-cache supports byte, half-word, and word accesses.

#### 4.1 D-Cache Operation

If the D-cache is enabled (C\_CP15 = 1), it is searched whenever the processor performs a data load or store. If the cache hits on a load, data is returned to the core regardless of the C\_MMU bit. If a cache read misses, the C\_MMU bit is examined. If it is 1, a line fetch is performed and the line is written to the cache following an LRU (least recently used) replacement algorithm. If C\_MMU is 0, a single external access is performed and the cache is not updated. Stores that hit the D-cache always update it, regardless of the C\_MMU bit, to keep the D-cache contents consistent with the external memory. Stores that miss do not update the D-cache (see Table 1).

| C_CP15 | C_MMU | B_MMU | unctional Description                                                  |  |  |  |

|--------|-------|-------|------------------------------------------------------------------------|--|--|--|

| 0      | Х     | Х     | No cache search                                                        |  |  |  |

| 1      | 0     | х     | Cache search active                                                    |  |  |  |

|        |       |       | Read and write misses are not cached.                                  |  |  |  |

|        |       |       | Cache serves read hits.                                                |  |  |  |

|        |       |       | Write hits update the cache.                                           |  |  |  |

|        |       |       | <ul> <li>Read misses and writes generate external accesses.</li> </ul> |  |  |  |

Table 1. Data Cache Configuration

| C_CP15 | C_MMU | B_MMU | Functional Description                                                                          |

|--------|-------|-------|-------------------------------------------------------------------------------------------------|

| 1      | 1     | 0     | Cache search active: write-through mode (WT)                                                    |

|        |       |       | <ul> <li>Read hits do not generate external accesses.</li> </ul>                                |

|        |       |       | <ul> <li>Write hits update the cache and the external memory.</li> </ul>                        |

|        |       |       | Read misses cause a line load.                                                                  |

|        |       |       | Write misses generate external accesses.                                                        |

| 1      | 1     | 1     | Cache search active: copy-back mode (CB)                                                        |

|        |       |       | <ul> <li>Read and write hits do not perform external accesses.</li> </ul>                       |

|        |       |       | Read misses cause a line load.                                                                  |

|        |       |       | <ul> <li>Write misses do not update the cache, and they generate an external access.</li> </ul> |

Table 1.

Data Cache Configuration (Continued)

If  $C_CP15 = 0$ , the D-cache is disabled and it is not searched. If a memory region is changed from cacheable to noncacheable and data must come from external memory, the cache must be flushed.

#### 4.2 Validity

The D-cache always requires that the MMU be enabled, so virtual addresses are always in use. The TLB descriptors in memory can be cached or not cached. When software is switching virtual address maps, it is necessary to invalidate the data cache so that the wrong data value is not returned (that is, so that a false D-cache hit does not occur). To do this, the CP15 register allows software to invalidate the entire D-cache. As noted before, disabling the D-cache and reenabling it does not invalidate it.

If the CB mode is used (see Table 1), software must first clean the cache to make it coherent with main memory (this is not necessary in the WT mode, because main memory is continuously updated as the data cache is used).

For CB mode, the VIVT (Virtual Index Virtual Tag) algorithm must be used if software is to avoid missing interrupts during the clean operation. Timer interrupts, for example, can be missed.

To avoid missing timer interrupts, the hardware clean operation can be interrupted for the software algorithm to check the min/max registers (CP15 registers) to determine if the clean operation has completed. If not, it must repeat the operation until complete.

#### Note:

Cleaning (discarding cache data completely) is not the same as flushing (temporarily cleaning a cache by writing data to disk or out-of-cache memory).

The entire D-cache can be invalidated with a single flush D-cache instruction through the CP15 cache operation register. The D-cache is flushed upon reset.

If the D-cache is disabled, its content is maintained valid and is accessible when the cache is reenabled.

#### 4.3 Double-Mapped Space

The D-cache works with virtual addresses, and it is assumed that every virtual address maps to a different physical address. If more than one virtual address corresponds to the same physical location, the cache cannot maintain its consistency because each virtual address has a separate entry in the cache and only one entry is updated on a processor write operation. To avoid any cache inconsistency, double-mapped virtual addresses must be marked as un-cacheable.

#### 5 Write Buffer

The write buffer (WB) increases system performance and can buffer up to seventeen 32-bit words of data. The MMU attributes B (B\_MMU) and C (C\_MMU) (which are part of the TLB descriptor) and the CP15 control register W bit (W\_CP15) control WB behavior.

Clearing W\_CP15 and C\_CP15 upon reset ensures that all accesses are nonbufferable until the MMU is enabled. To use the write buffer, MMU must be enabled. The write buffer is always disabled when the MMU is off. However, the two functions can be enabled simultaneously with a single write to the CP15 control register.

Clearing bit 3 in the CP15 control register disables the write buffer. Any writes already in the write buffer complete normally.

It is not possible to abort buffered writes externally, because the s\_abort external signal is ignored and data is simply discarded. Areas of memory that can generate aborts must be marked as unbufferable in the MMU page tables.

#### 5.1 Operation

The WB operation is controlled by four control bits, as shown in Table 2.

| C_CP15 | W_CP15 | С_ММИ | B_MMU | Functional Description                   |

|--------|--------|-------|-------|------------------------------------------|

| 0      | 0      | Х     | х     |                                          |

| 0      | 1      | х     | 0     | Writes are not buffered.                 |

| 1      | 0      | Х     | x     | See Note                                 |

| 1      | 1      | 0     | 0     |                                          |

| 0      | 1      | х     | 1     | Non-cacheable, buffered (NCB)            |

| 1      | 1      | 0     | 1     | NCB                                      |

| 1      | 1      | 1     | 0     | Writes are buffered, write-through mode. |

| 1      | 1      | 1     | 1     | Writes are buffered, copy-back mode.     |

Table 2.Write Buffer Configuration

**Note:** In copy-back mode with the WB disabled (1011 configuration), dirty lines are saved to the external memory via the WB regardless of W\_CP15. Write misses go directly to the external memory. If the WB is disabled and the system is configured in copy-back mode, only write misses stall the system.

When writes are not buffered, the processor stalls until the external write access is complete.

#### 5.2 SWAP Instruction

When bit L of the CP15 TI925T configuration register is set, the write phase of the SWAP instruction (interlocked read-write) is treated as unbuffered when data belongs to a non-cacheable, non-buffered (NCNB) or NCB region, even if it is marked as buffered. The S\_LOCK signal is active through the read and write accesses. If the read of the SWAP instruction hits the cache, S\_LOCK is asserted during the read despite the fact that no external access is performed. The write is performed both in the cache and externally with S\_LOCK active.

For WT- or CB-mode regions, S\_LOCK is not active and accesses are performed like ordinary read or write accesses.

When bit L of the CP15 TI925T configuration register is reset, S\_LOCK stays low during the SWAP instruction regardless of the memory region type (NCNB,

NCB, WT, or CB). If marked as buffered, data is written to the write buffer and reaches the system bus after an undetermined delay.

#### 6 Coprocessor 15

TI925T operation and configuration are controlled with coprocessor instructions, configuration pins, and the MMU translation tables. The co-processor instructions manipulate on-chip registers, which control the configuration of the cache memories, write buffer, MMU, and a number of other options described in the following sections.

#### 6.1 CP15 Access

The CP15 defines 16 registers. Table 3 shows the registers available for reading and for writing. While most registers are used to control various operations, some, such as register 0, only provide information. MRC and MCR instructions can access CP15 registers in privileged mode only. Figure 2 contains the instruction bit pattern of the MCR and MRC instructions.

| 31 |      | 28 | 27 |      | 24 | 23 | 22     | 21        | 20 | 19 | 18 | 17 | 16 |

|----|------|----|----|------|----|----|--------|-----------|----|----|----|----|----|

|    | Cond |    |    | 1110 |    | 0  | pcode_ | _1        | L  |    | CF | Rn |    |

|    |      |    |    |      |    |    |        |           |    |    |    |    |    |

| 45 |      | 10 |    |      | 0  | 7  |        | F         | 4  | 0  |    |    | 0  |

| 15 |      | 12 | 11 |      | 8  | 1  |        | 5         | 4  | 3  |    |    | 0  |

|    | Rd   |    |    | 1111 |    | 0  | pcode_ | ode_2 1 C |    | CF | Rm |    |    |

Figure 2. MRC, MCR Bit Pattern

The CRn field specifies the coprocessor register to access. The CRm field and opcode\_2 fields specify a particular action when addressing some registers or shadow registers. The TI925T takes the undefined instruction trap upon executing CDP, LDC, STC, and unprivileged MCR/MRC instructions on CP15.

#### 6.2 Register Descriptions

The following terms and abbreviations are used throughout the register descriptions:

- Unpredictable (UNP): Reading from such a location returns data of unpredictable value. Writing to this location causes unpredictable behavior or an unpredictable change in device configuration.

- Undefined (UND): Any access to such registers makes TI925T take the undefined instruction trap.

- Should be zero (SBZ): All bits written to this field must be 0.

- Ignored: Writing to such a location does not affect the system behavior.

- U VA: Virtual address (data or instruction)

In all cases, reading data values from or writing any data values to any CP15 register, including those fields specified as unpredictable or SBZ, causes no permanent damage to the TI925T.

| Register | Reads                  | Writes                 | Access            | RD   |

|----------|------------------------|------------------------|-------------------|------|

| 0        | ID register            | Ignored                | Read-only         | 310  |

| 1        | Control register       | Control register       | Read/Modify/Write | 140  |

| 2        | Translation table base | Translation table base | Read/Write        | 3114 |

| 3        | Domain access control  | Domain access control  | Read/Write        | 310  |

| 4        | Unpredictable          | Ignored                |                   | -    |

| 5        | Fault status           | Fault status           | Read/Write        | 80   |

| 6        | Fault address          | Fault address          | Read/Write        | 310  |

| 7        | Unpredictable          | Cache operations       | Write-only        | 310  |

| 8        | Unpredictable          | TLB operations         | Write-only        | 310  |

| 9        | Unpredictable          | Ignored                |                   | -    |

| 10       | TLB lock-down          | TLB lock-down          | Read/Write        | 310  |

| 11       | Unpredictable          | Ignored                |                   | -    |

| 12       | Unpredictable          | Ignored                |                   | -    |

| 13       | PID                    | PID                    | Read/Write        | 3125 |

| 14       | Unpredictable          | Ignored                |                   | -    |

| 15       | TI operations          | TI operations          | Read/Write        | 310  |

Table 3. CP15 Register Summary

#### 6.2.1 ID Register and Cache Information Register

Reading from CP15 register 0 returns either an identification defined by architecture and implementation for the processor or information on the cache, depending on the op-code\_2 used. CRm should be zero (SBZ) when reading.

Writing to register 0 is ignored.

| Function             | Opcode_2 | CRm    | Rd         | Instruction               |

|----------------------|----------|--------|------------|---------------------------|

| Read ID <sup>†</sup> | 0bXXX    | 0bXXXX | TI925T ID  | MRC p15, 0, Rd, c0, c0, 0 |

| Read CIR             | 0b001    | 0b0000 | Cache info | MRC p15, 0, Rd, c0, c0, 1 |

#### Table 4. Reading From CP15 Register 0

<sup>†</sup> All opcodes [opcode\_2,CRm] except [1,0] return the TI925T ID.

#### Table 5. CP15 ID Register

| Bits  | Field                | Description                                                                                                                                                 |

|-------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–24 | Implementers         | Contains the ASCII code of the implementer trademark (0x54 = Texas Instruments)                                                                             |

| 23–16 | Architecture version | Contains the architecture version (0x02 Version v4T)                                                                                                        |

| 15–4  | Part number          | Contains a 3-digit part number in binary-coded decimal format. The OS bit O in the TI925T configuration register sets the value of these fields as follows: |

|       |                      | 915 in Tl925T mode<br>925 in Windows CE mode                                                                                                                |

| 3–0   | Reserved             | Contains the microprocessor revision number 2                                                                                                               |

#### Table 6. CP15 Cache Information Register (CIR)

| Bits  | Field               | Value | Description                                                                                                                                                                                                                                                                                                                                         |

|-------|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–29 | Reserved            | 0     | Read as 0.                                                                                                                                                                                                                                                                                                                                          |

| 28–25 | Cache type          |       | Cache type: read as 0010. The cache provides clean-cache<br>entry and flush-cache-entry with a cache index in addition to<br>operations with a virtual address (also called clean-cache-step<br>or flush-cache-step). The format of the clean-cache-entry is<br>given in the <i>Register 7: Cache Operations</i> section later in this<br>document. |

| 24    | ID                  | 0     | Unified I-/D-cache                                                                                                                                                                                                                                                                                                                                  |

|       |                     | 1     | Harvard cache                                                                                                                                                                                                                                                                                                                                       |

| 23–21 | Reserved            | 0     | Read as 0.                                                                                                                                                                                                                                                                                                                                          |

| 20–18 | D-cache information |       | Base value of D-cache size (same format as for I-cache)                                                                                                                                                                                                                                                                                             |

| 17–15 | D-cache information |       | Base value of D-cache associativity (same format as for I-cache)                                                                                                                                                                                                                                                                                    |

| Bits  | Field               | Value | Description                                                                                                                                                                                                        |

|-------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14    | D-Cache information |       | Parameter to calculate the real D-cache associativity and size:                                                                                                                                                    |

|       |                     | 0     | D-cache associativity and D-cache size = base value                                                                                                                                                                |

|       |                     | 1     | D-cache associativity and D-cache size = 3/2 of the base value.<br>Exception: If base value of associativity is 1, a 1 indicates that<br>there is no D-cache and 0 indicates that D-cache is really<br>direct-map. |

| 13–12 | D-cache information |       | Indicate line length of D-cache (same format as for I-cache)                                                                                                                                                       |

| 11–9  | Reserved            | 0     | Read as 0.                                                                                                                                                                                                         |

| 8–6   | I-cache information |       | Base value of I-cache size:                                                                                                                                                                                        |

|       |                     | 0000  | 512 bytes                                                                                                                                                                                                          |

|       |                     | 0001  | 1K byte                                                                                                                                                                                                            |

|       |                     | 0010  | 2K bytes                                                                                                                                                                                                           |

|       |                     | 0011  | 4K bytes                                                                                                                                                                                                           |

|       |                     | 0100  | 8K bytes                                                                                                                                                                                                           |

|       |                     | 0101  | 16K bytes                                                                                                                                                                                                          |

|       |                     | 0110  | 32K bytes                                                                                                                                                                                                          |

|       |                     | 0111  | 64K bytes                                                                                                                                                                                                          |

|       |                     |       | Note: 2 (bits $8-6$ – bits $5-3$ – bits $1-0$ ) gives the number of lines.                                                                                                                                         |

| 5–3   | I-cache information |       | Base value of I-cache associativity:                                                                                                                                                                               |

|       |                     | 0000  | Direct map                                                                                                                                                                                                         |

|       |                     | 0001  | 2-way associative                                                                                                                                                                                                  |

|       |                     | 0010  | 4-way associative                                                                                                                                                                                                  |

|       |                     | 0011  | 8-way associative                                                                                                                                                                                                  |

|       |                     | 0100  | 16-way associative                                                                                                                                                                                                 |

|       |                     | 0101  | 32-way associative                                                                                                                                                                                                 |

|       |                     | 0110  | 64-way associative                                                                                                                                                                                                 |

|       |                     | 0111  | 128-way associative                                                                                                                                                                                                |

#### Table 6. CP15 Cache Information Register (CIR) (Continued)

| Bits | Field               | Value | Description                                                                                                                                                                                                                           |

|------|---------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2    | I-cache information |       | Parameter to calculate the real I-cache associativity and size:                                                                                                                                                                       |

|      |                     | 0     | I-cache associativity and I-cache size are equal to the base value.                                                                                                                                                                   |

|      |                     | 1     | I-cache associativity and I-cache size are equal to 3/2 of the<br>base value. Exception: If base value of associativity is 1, a 1<br>indicates here that there is no I-cache; 0 indicates that the<br>I-cache is really a direct-map. |

| 1–0  | I-cache information |       | Indicates line length of the I-cache:                                                                                                                                                                                                 |

|      |                     | 00    | 8 bytes                                                                                                                                                                                                                               |

|      |                     | 01    | 16 bytes                                                                                                                                                                                                                              |

|      |                     | 10    | 32 bytes                                                                                                                                                                                                                              |

|      |                     | 11    | 64 bytes                                                                                                                                                                                                                              |

#### Table 6. CP15 Cache Information Register (CIR) (Continued)

The cache information register specifies the configuration of the TI925T core. It is recommended that the register be written using a read-modify-write routine.

Reading from CP15 register 1 reads the control bits. The CRm and opcode\_2 fields are ignored when reading CP15 register 1, but must be zero.

Writing to CP15 register 1 sets the control bits. The CRm and opcode\_2 fields are not used when writing CP15 register 1, but must be zero.

All control bits but V are set to zero upon reset.

| Table 7. | CP15 Control Register |

|----------|-----------------------|

|----------|-----------------------|

| Bits  | Field | Value | Description                                                                                                                                                                                                                                                                  |

|-------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–15 |       |       | Reserved: These bits should not be relied upon for any particular value<br>in these bit locations during a read (they should be masked properly).<br>These bits should be written as zero.                                                                                   |

| 14    |       | 0     | Read as 0. Write is ignored.                                                                                                                                                                                                                                                 |

| 13    | V     |       | Alternate vector select. Sets the address of the exception vector from address 0x00000000 to 0x0000001F when at zero and from 0xFFFF0000 to 0xFFFF001F when at 1. This bit takes the value of the HIVECS signal port upon reset. After reset, it can be changed by software. |

| Bits  | Field | Value | Description                                                                                                                                                                                                    |

|-------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12    | 1     |       | Instruction cache enable/disable                                                                                                                                                                               |

|       |       | 0     | Instruction cache disabled                                                                                                                                                                                     |

|       |       | 1     | Instruction cache enabled                                                                                                                                                                                      |

| 11–10 |       | 0     | Read as 0. Write is ignored.                                                                                                                                                                                   |

| 9     | R     |       | ROM protection. This bit modifies the MMU protection system (see Table 24).                                                                                                                                    |

| 8     | S     |       | System protection. This bit modifies the MMU protection system (see Table 24).                                                                                                                                 |

| 7     | В     |       | Little/big endian configuration. The TI925T on the OMAP5910 device supports only little endian mode due to the system architecture of the device. This bit must always be written as 0.                        |

|       |       | 0     | Little endian                                                                                                                                                                                                  |

|       |       | 1     | Reserved (do not use)                                                                                                                                                                                          |

| 6–4   |       | 1     | Read as 1. Write is ignored.                                                                                                                                                                                   |

| 3     | W     |       | Write buffer enable/disable                                                                                                                                                                                    |

| 2     | С     |       | Data cache enable/disable                                                                                                                                                                                      |

|       |       | 0     | Data cache disabled                                                                                                                                                                                            |

|       |       | 1     | Data cache enabled                                                                                                                                                                                             |

| 1     | А     |       | Alignment fault enable/disable                                                                                                                                                                                 |

|       |       | 0     | Address alignment fault checking disabled                                                                                                                                                                      |

|       |       | 1     | Address alignment fault checking enabled                                                                                                                                                                       |

|       |       |       | Note: The alignment is checked only on data; code alignment is always<br>on a 32-bit boundary. If address alignment fault is enabled, words must<br>be word-aligned, and half-words must be half-word-aligned. |

Table 7. CP15 Control Register (Continued)

| Bits | Field | Value | Description                                                                                                                                                                                                                                                 |

|------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | М     |       | Memory management unit (MMU) enable/disable                                                                                                                                                                                                                 |

|      |       | 0     | MMU disabled                                                                                                                                                                                                                                                |

|      |       | 1     | MMU enabled                                                                                                                                                                                                                                                 |

|      |       |       | The MMU must be enabled before or at the same time as the data cache (C) and write buffer (W). The instruction cache can be enabled independently. When the MMU is disabled and no address translation occurs, the D-cache and write buffer are forced OFF. |

#### Table 7. CP15 Control Register (Continued)

#### Note:

Care must be taken if the translated address differs from the non-translated address, because the instructions following the enabling of the MMU are fetched using no address translation. Enabling the MMU may be considered as an instruction with delayed execution. A similar situation occurs when the MMU is disabled.

The following code segment example shows correct MMU enabling which takes into account the latency to transition to virtual addressing:

```

ldr r0, =bVirtualStart; Load r0 with virtual jump

location; Enable the MMU.

mrc p15, 0, r1, c1, c0, 0; Read the control register.

orr r1, r1, #BIT0; Set the M bit to enable MMU.

nop

mcr p15, 0, r1, c1, c0, 0; Write the control register.

mov pc, r0; Jump to the virtual address.

nop

bVirtualStart

nop

nop

```

The MMU, I-cache, and D-cache can be enabled or disabled independently. If the data cache or write buffer are enabled when the MMU is not enabled, the data cache and the write buffer stay off, preventing invalid combinations.

The functions MMU, D-cache, I-cache, and WB can be enabled simultaneously with a single write to the control register.

| Figure 3. Format of the CP15 Translation Table Base Register |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

| 31 14                  | 4 | 13      | 0 |

|------------------------|---|---------|---|

| Translation Table Base |   | UNP/SBZ |   |

Reading from CP15 register 2 returns the pointer to the currently active first-level translation table in bits 31-14 and an unpredictable value in bits 13-0. The CRm and opcode 2 fields are SBZ when reading this register.

Writing to CP15 register 2 updates the pointer to the currently active first-level translation table from the value in bits 31-14 of the written value. Bits 13-0 must be written as zero. The CRm and opcode\_2 fields are SBZ when writing to this register.

#### Figure 4. Format of the CP15 Domain Access Control Register

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| D1 | 5  | D  | 14 | D  | 13 | D  | 12 | D  | 11 | D  | 10 | D  | 9  | D  | 8  |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| D7 | 7  | D  | 6  | D  | 5  | D  | 4  | D  | 3  | D  | 2  | D  | 1  | D  | 0  |

Reading from CP15 register 3 returns the value of the domain access control register. The CRm and opcode\_2 fields are SBZ when reading this register.

Writing to CP15 register 3 writes the value of the domain access control register.

The CRm and opcode\_2 fields are SBZ when writing to this register.

The domain access control register consists of sixteen two-bit fields, each defining the access permissions for one of the 16 domains (D15-D0). Table 8 gives more details on the meaning of each field.

Data, instructions, or both can use each of these domains. Two basic kinds of users are supported: clients and managers.

| Value | Access Type | Description                                                                    |

|-------|-------------|--------------------------------------------------------------------------------|

| 0b00  | No access   | Any access generates a domain fault.                                           |

| 0b01  | Client      | Access rights are checked against the permission given by the page descriptor. |

| 0b10  | Reserved    | Behaves like no access                                                         |

| 0b11  | Manager     | The access rights are not checked; permission faults cannot be generated.      |

Table 8.Domain Configuration

Reading CP15 register 5 returns the value of the fault status register (FSR). The FSR contains the source of the last data fault. Only the bottom 9 bits are returned. The top 23 bits are unpredictable. The FSR indicates the domain and type of access being attempted when an abort occurred.

Table 9. CP15 Fault Status Register

| Bits | Field  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–9 | UNP/SB | Reserved: The values in these particular bit locations cannot be relied upon during a read (they must be masked properly). These bits should be written as zero.                                                                                                                                                                                                                                                                                                                                           |

| 8    | 0      | Read as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7–4  | Domain | Specify which of the 16 domains (D15-D0) was being accessed when the last fault occurred.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3–0  | Status | Indicate the type of fault due to the last access being attempted. The encoding of these bits is shown in Table 23, <i>Priority Encoding of the Fault Status Register</i> .                                                                                                                                                                                                                                                                                                                                |

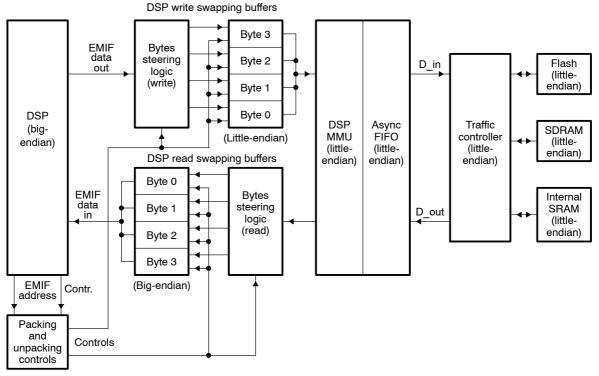

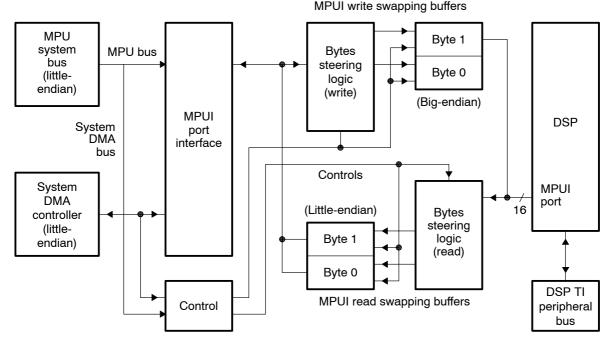

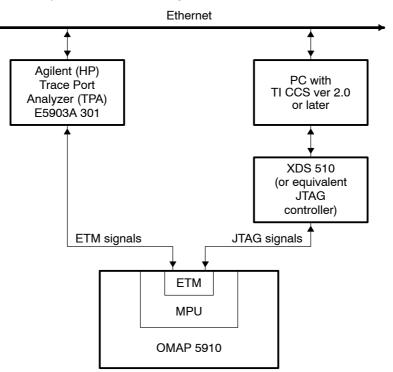

|      |        | The FSR is only updated for data access faults, not for instruction fetch faults. When a fault occurs during a load or store multiple (LDM or STM instructions), the FSR records the domain corresponding to the first fault caused by LDM or STM. For example, an LDM performing 12 accesses may cross a page boundary with, say, four accesses in one page and eight in the next page. If accessing the second page causes an abort, the FSR and FAR record the information related to the fifth access. |