# **ARM 7500FE**

# **Data Sheet**

Document Number: ARM DDI 0077B Issued: September 1996 Copyright Advanced RISC Machines Ltd (ARM) 1996 All rights reserved

#### ENGLAND

Advanced RISC Machines Limited 90 Fulbourn Road Cherry Hinton Cambridge CB1 4JN UK Telephone: +44 1223 400400 Facsimile: +44 1223 400410 Email<sup>.</sup> info@armltd.co.uk

#### JAPAN

Advanced RISC Machines K.K. KSP West Bldg, 3F 300D, 3-2-1 Sakado Takatsu-ku, Kawasaki-shi Kanagawa 213 Japan +81 44 850 1301 Telephone: Facsimile: +81 44 850 1308 Email: info@armltd.co.uk

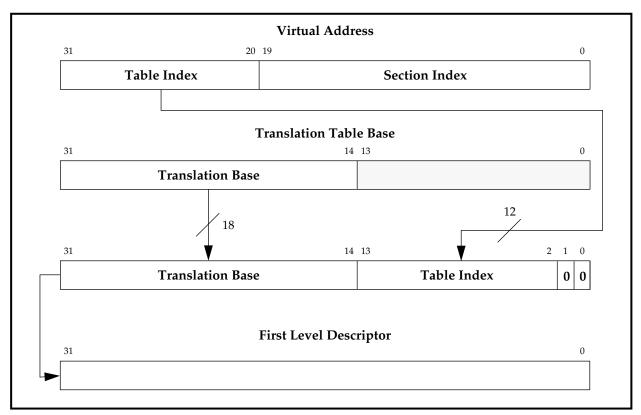

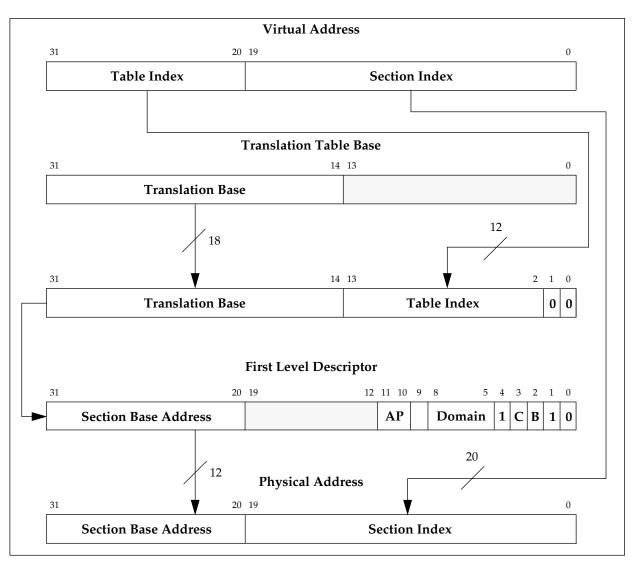

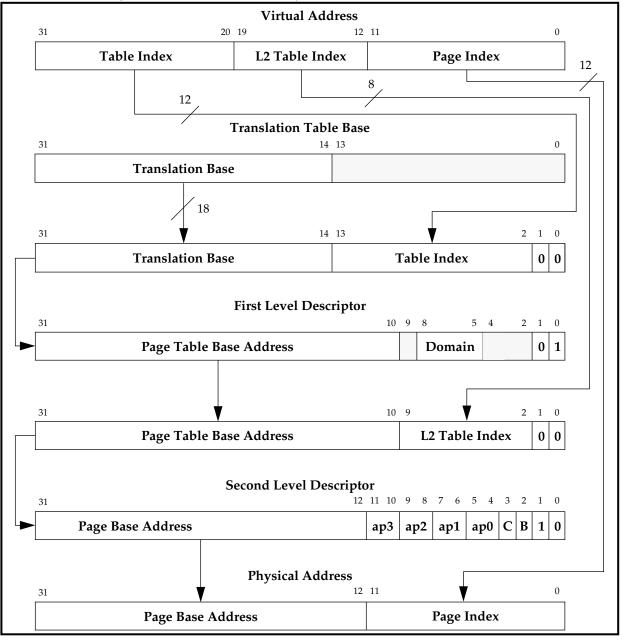

#### GERMANY

Advanced RISC Machines Limited Otto-Hahn Str. 13b 85521 Ottobrunn-Riemerling Munich Germany Telephone: +49 89 608 75545 Facsimile: +49 89 608 75599 Email<sup>.</sup> info@armltd.co.uk

USA ARM USA Incorporated

Suite 5 985 University Avenue Los Gatos CA 95030 USA Telephone: +1 408 399 5199 Facsimile: +1 408 399 8854 Email: info@arm.com

World Wide Web address: http://www.arm.com

# **Open Access - Preliminary**

#### **Proprietary Notice**

ARM, the ARM Powered logo, BlackICE and ICEbreaker are trademarks of Advanced RISC Machines Ltd.

Neither the whole nor any part of the information contained in, or the product described in, this specification may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this specification is subject to continuous developments and improvements. All particulars of the product and its use contained in this datasheet are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties or merchantability, or fitness for purpose, are excluded.

This datasheet is intended only to assist the reader in the use of the product. ARM Ltd shall not be liable for any loss or damage arising from the use of any information in this datasheet, or any error or omission in such information, or any incorrect use of the product.

#### Key

#### **Document Number**

This document has a number which identifies it uniquely. The number is displayed on the front page and at the foot of each subsequent page.

(On review drafts only) Two-digit draft number Release code in the range A-Z Unique four-digit number Document type

#### **Document Status**

The document's status is displayed in a banner at the bottom of each page. This describes the document's confidentiality and its information status.

Confidentiality status is one of:

| ARM Confidential              | Distributable to ARM staff and NDA signatories only                         |

|-------------------------------|-----------------------------------------------------------------------------|

| Named Partner Confidential    | Distributable to the above and to the staff of named partner companies only |

| Partner Confidential          | Distributable within ARM and to staff of all partner companies              |

| Open Access                   | No restriction on distribution                                              |

| Information status is one of: |                                                                             |

| Advance                       | Information on a potential product                                          |

| Preliminary                   | Current information on a product under development                          |

| Final                         | Complete information on a developed product                                 |

#### Change Log

| Issue | Date     | By  | Change                                   |

|-------|----------|-----|------------------------------------------|

| A     | Aug 1996 | SKW | Released as preliminary version          |

| B-01  | Sep 1996 | SKW | Amendments and update to general release |

Preface-ii

# Preface

ARM7500FE is a highly integrated, multi-media single-chip computer, based around the ARM RISC microprocessor macrocell. ARM7500FE contains all the functionality required to create a complete computing system with the minimum of external components. The wide range of features incorporated into ARM7500FE makes it an extremely flexible device, which can be programmed according to the required application to optimise for high performance or low power, or a combination of both.

#### Features

- Highly integrated RISC computer

- 36.3 Dhrystone 2.1 MIPS ARM7 core @ 40MHz CPU clock

- 5.7 million SAXPY loops, or up to 6 double-precision Linpack MFLOPS (at 40MHz)

- 4 Kbyte combined instruction and data cache

- Flexible Memory Management Unit

- Glueless memory interface (16 or 32 bits wide) for ROM, RAM and EDO DRAM

- 128 MBytes/sec (peak) memory bandwidth using 64MHz memory clock

- 3 channel DMA controller (for video, cursor and sound data)

- I/O controller, including PC-style bus

- 2 serial ports, 4 A/D channels

- 32-bit CD quality serial sound channel

- Video controller with up to 120MHz pixel clock; resolutions up to 1024 x 768 pixels

- 16 million colours from 256-entry palette, and 16-level grey scales for LCD displays

- Direct RGB drive of CRTs; support for interlaced TV displays

- Suspend and stop power-saving modes

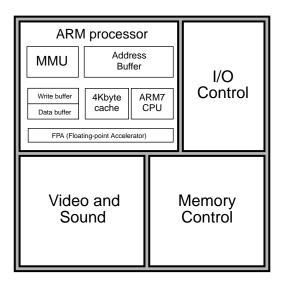

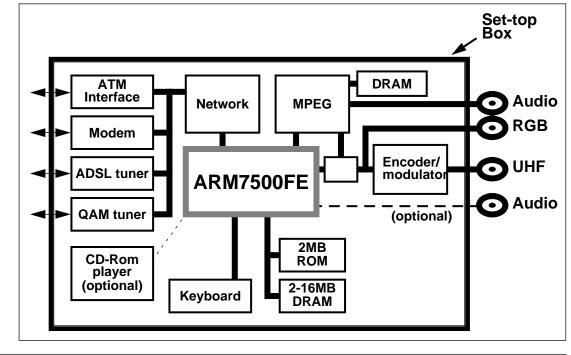

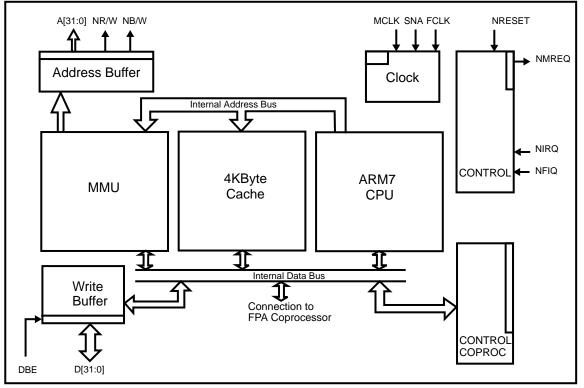

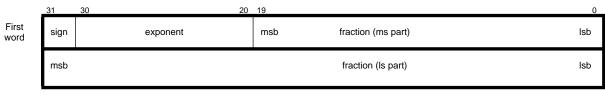

#### Block diagram of the ARM7500FE

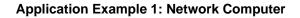

#### Applications

ARM7500FE is ideally suited to applications requiring a compact, low-cost, power-efficient, high-performance, RISC computing system on a single chip. These include:

MultimediaInternet appliances and set-top boxes (see page iv)Portable ComputingHandheld test instrumentationGames consolesDesktop computing

Preface-iii

ARM7500FE Data Sheet ARM DDI 0077B

# Preface

Application Example 2: Set-top Box for Digital Interactive Television

ARM7500FE Data Sheet ARM DDI 0077B ARM

#### Preface-iv

**Open Access - Preliminary**

# Preface

#### **Datasheet Notation**

| 0x     | marks a Hexadecimal quantity                                                      |

|--------|-----------------------------------------------------------------------------------|

| BOLD   | external signals are shown in bold capital letters                                |

| binary | where it is not clear that a quantity is binary it is followed by the word binary |

ARM7500FE Data Sheet ARM DDI 0077B

**Open Access - Preliminary**

Preface-vi

# Contents

| 1 | Intro | duction                                   | 1-1  |

|---|-------|-------------------------------------------|------|

|   | 1.1   | Introduction                              | 1-2  |

|   | 1.2   | Functional Block Diagram                  | 1-2  |

|   | 1.3   | ARM Processor Macrocell                   | 1-2  |

|   | 1.4   | FPA Macrocell                             | 1-2  |

|   | 1.5   | Video and Sound Macrocell                 | 1-4  |

|   | 1.6   | Clock Control and Power Management        | 1-4  |

|   | 1.7   | Memory System                             | 1-5  |

|   | 1.8   | Other Features                            | 1-6  |

|   | 1.9   | Test Modes                                | 1-6  |

|   | 1.10  | Structure of ARM7500FE                    | 1-7  |

|   | 1.11  | Resetting ARM7500FE Systems               | 1-7  |

| 2 | Sign  | al Description                            | 2-1  |

|   | 2.1   | Signal Description for ARM7500FE          | 2-3  |

| 3 | The   | ARM Processor Macrocell                   | 3-1  |

|   | 3.1   | Introduction                              | 3-2  |

|   | 3.2   | Instruction Set                           | 3-2  |

|   | 3.3   | Memory Interface                          | 3-3  |

|   | 3.4   | Clocks and Synchronous/Asynchronous Modes | 3-3  |

|   | 3.5   | ARM Processor Block Diagram               | 3-4  |

| 4 | The   | ARM Processor Programmers' Model          | 4-1  |

|   | 4.1   | Introduction                              | 4-2  |

|   | 4.2   | Register Configuration                    | 4-2  |

|   | 4.3   | Operating Mode Selection                  | 4-4  |

|   | 4.4   | Registers                                 | 4-5  |

|   | 4.5   | Exceptions                                | 4-8  |

|   | 4.6   | Configuration Control Registers           | 4-13 |

**Open Access - Preliminary**

ARM DDI 0077B

| 5 | ARM Processor Instruc                                                                                                                                                                                                                                                                                                                                                                | tion Set                                                                                                                                                                               | 5-1                                                                                                                       |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|   | <ul> <li>5.7 Single Data Transfer</li> <li>5.8 Block Data Transfer (1</li> <li>5.9 Single Data Swap (S)</li> <li>5.10 Software Interrupt (S)</li> <li>5.11 Coprocessor Instruction</li> <li>5.12 Coprocessor Data Op</li> <li>5.13 Coprocessor Data Transfer</li> <li>5.14 Coprocessor Register</li> <li>5.15 Undefined Instruction</li> <li>5.16 Instruction Set Example</li> </ul> | ith Link (B, BL)<br>MSR)<br>Accumulate (MUL, MLA)<br>(LDR, STR)<br>LDM, STM)<br>VP)<br>VI)<br>ons on the ARM Processor<br>erations (CDP)<br>ansfers (LDC, STC)<br>Transfers (MRC, MCR) | 5-2<br>5-3<br>5-4<br>5-13<br>5-16<br>5-18<br>5-24<br>5-32<br>5-34<br>5-36<br>5-36<br>5-36<br>5-38<br>5-41<br>5-43<br>5-44 |

| 6 | 5.17 Instruction Speed Sur<br>Cache, Write Buffer and                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                        | 5-47<br><b>6-1</b>                                                                                                        |

| - | <ul> <li>6.1 Instruction and Data (</li> <li>6.2 Read-Lock-Write</li> <li>6.3 IDC Enable/Disable a</li> <li>6.4 Write Buffer (Wb)</li> <li>6.5 Coprocessors</li> </ul>                                                                                                                                                                                                               | Cache (IDC)                                                                                                                                                                            | 6-2<br>6-3<br>6-3<br>6-3<br>6-3<br>6-5                                                                                    |

| 7 | ARM Processor MMU                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                        | 7-1                                                                                                                       |

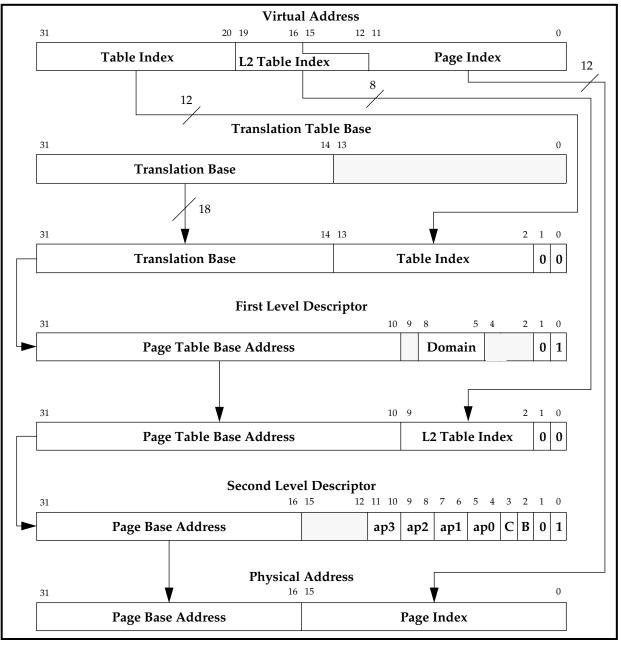

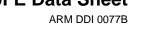

|   | <ul> <li>7.1 Introduction</li> <li>7.2 MMU Program-access</li> <li>7.3 Address Translation</li> <li>7.4 Translation Process</li> <li>7.5 Translating Section R</li> <li>7.6 Translating Small Pag</li> <li>7.7 Translating Large Pag</li> <li>7.8 MMU Faults and CPU</li> </ul>                                                                                                      | eferences<br>je References<br>je References<br>Aborts<br>Status Registers (FAR & FSR)<br>ol                                                                                            | 7-2<br>7-4<br>7-4<br>7-8<br>7-10<br>7-11<br>7-12<br>7-12<br>7-12<br>7-13<br>7-14<br>7-16<br>7-17                          |

| 8 | The FPA Coprocessor I                                                                                                                                                                                                                                                                                                                                                                | Macrocell                                                                                                                                                                              | 8-1                                                                                                                       |

|   | <ul><li>8.1 Overview</li><li>8.2 FPA Functional Block</li><li>8.3 FPA Block Diagram</li></ul>                                                                                                                                                                                                                                                                                        | S                                                                                                                                                                                      | 8-2<br>8-3<br>8-5                                                                                                         |

| 9 Flo                                                                                                                        | ating-Point Coprocessor Programmer's Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9-1                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5                                                                                              | Overview<br>Floating-Point Operation<br>ARM Integer and Floating-Point Number Formats<br>The Floating-Point Status Register (FPSR)<br>The Floating-Point Control Register (FPCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9-2<br>9-2<br>9-4<br>9-8<br>9-11                                                                                                                                                                                                                                                 |

| 10 Flo                                                                                                                       | ating-Point Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10-1                                                                                                                                                                                                                                                                             |

| 10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6                                                                                 | <ul> <li>Floating-Point Coprocessor Data Operations (CPDO)</li> <li>Floating-Point Coprocessor Register Transfer (CPRT)</li> <li>FPA Instruction Set</li> <li>Floating-Point Support Code</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10-2<br>10-7<br>10-11<br>10-14<br>10-16<br>10-17                                                                                                                                                                                                                                 |

| 11 The                                                                                                                       | e Video and Sound Macrocell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11-1                                                                                                                                                                                                                                                                             |

| 11.1<br>11.2<br>11.3                                                                                                         | 2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11-2<br>11-2<br>11-4                                                                                                                                                                                                                                                             |

| 12 The                                                                                                                       | e Video and Sound Programmer's Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12-1                                                                                                                                                                                                                                                                             |

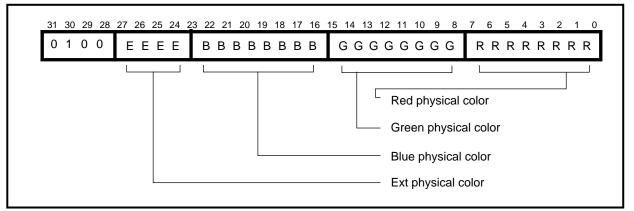

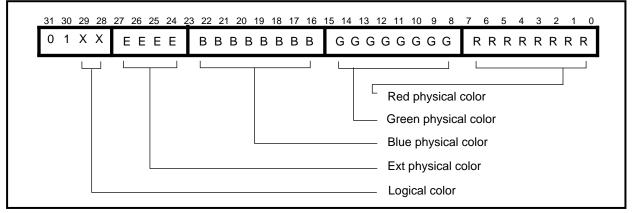

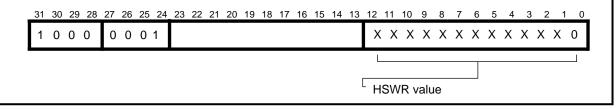

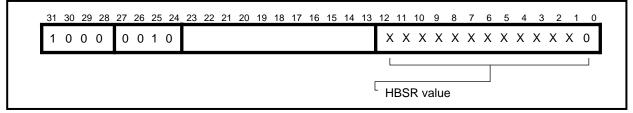

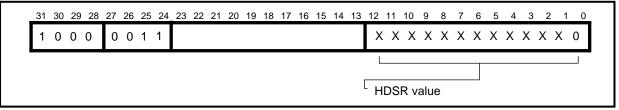

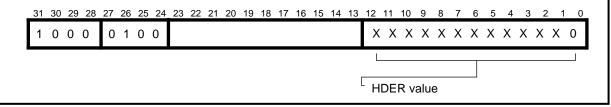

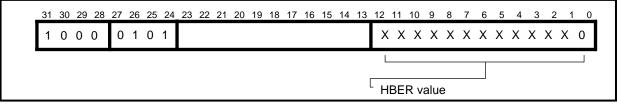

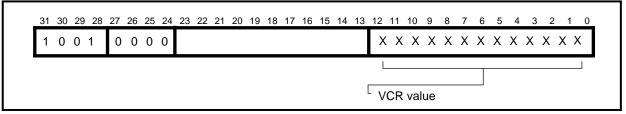

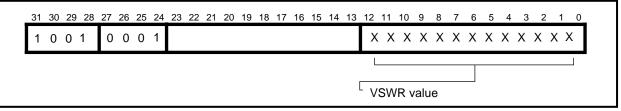

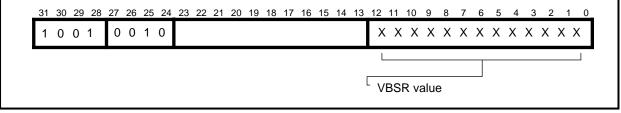

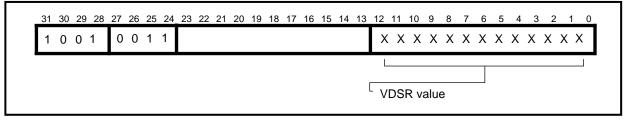

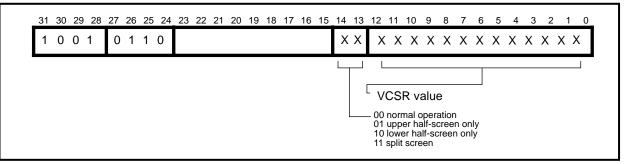

| 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6<br>12.7<br>12.8<br>12.9<br>12.1<br>12.1<br>12.1<br>12.1<br>12.1<br>12.1<br>12.1 | <ul> <li>Video Palette: Address 0x0</li> <li>Video Palette Address Pointer: Address 0x1</li> <li>LCD Offset Registers: Addresses 0x30 and 0x31</li> <li>Border Color Register: Address 0x4</li> <li>Cursor Palette: Addresses 0x5-0x7</li> <li>Horizontal Cycle Register (HCR): Address 0x80</li> <li>Horizontal Sync Width Register (HSWR): Address 0x82</li> <li>Horizontal Display Start Register (HDSR): Address 0x83</li> <li>Horizontal Display End Register (HDER): Address 0x84</li> <li>Horizontal Border End Register (HDER): Address 0x85</li> <li>Horizontal Interlace Register (HIR): Address 0x86</li> <li>Horizontal Test Register (VCR): Address 0x87</li> <li>Horizontal Test Register (VSWR): Address 0x90</li> <li>Vertical Sync Width Register (VDSR): Address 0x91</li> <li>Vertical Display End Register (VDSR): Address 0x93</li> <li>Vertical Display End Register (VDSR): Address 0x93</li> <li>Vertical Display End Register (VDSR): Address 0x94</li> <li>Vertical Display End Register (VDSR): Address 0x93</li> <li>Vertical Display End Register (VDSR): Address 0x94</li> <li>Vertical Display End Register (VCSR): Address 0x95</li> <li>Vertical Cursor Start Register (VCSR): Address 0x96</li> <li>Vertical Cursor End Register (VCSR): Address 0x97</li> <li>Vertical Cursor End Register (VCSR): Address 0x97</li> <li>Vertical Test Registers: Addresses 0x98, 0x9A &amp; 0x9C</li> <li>External register (conreg): Address 0x2</li> <li>Frequency Synthesizer Register (fsynreg): Address 0xD</li> <li>Control Register (conreg): Address 0xE</li> <li>Data Control Register (DCTL): Address 0xB0</li> </ul> | 12-3<br>12-5<br>12-5<br>12-6<br>12-7<br>12-7<br>12-8<br>12-8<br>12-8<br>12-9<br>12-9<br>12-9<br>12-10<br>12-10<br>12-10<br>12-10<br>12-10<br>12-10<br>12-11<br>12-11<br>12-11<br>12-12<br>12-13<br>12-13<br>12-13<br>12-13<br>12-13<br>12-14<br>12-15<br>12-16<br>12-17<br>12-17 |

| 13  | Video         | Macrocell Interface                                                | 13-          | 1  |

|-----|---------------|--------------------------------------------------------------------|--------------|----|

|     |               | Bus Interface                                                      | 13-          |    |

|     | 13.2          | Setting the FIFO Preload Value                                     | 13-          |    |

| 14  |               | Features                                                           | 14-          |    |

|     | 14.1          | Pixel Clock                                                        | 14-          |    |

|     |               | The Palette                                                        | 14-<br>14-   |    |

|     |               | Cursor<br>Hi-Res Support                                           | 14-          |    |

|     |               | Liquid Crystal Displays                                            | 14-          |    |

|     | 14.6          | External Support                                                   | 14-          |    |

|     | 14.7          | Analog Outputs                                                     | 14-1         | 2  |

| 15  | Sound         | l Features                                                         | 15-          | 1  |

|     | 15.1          | Sound                                                              | 15-          | ·2 |

|     |               | The Sound FIFO                                                     | 15-          |    |

|     | 15.3          | The Digital Serial Sound Interface                                 | 15-          | ·2 |

| 16  |               | ry and I/O Programmers' Model                                      | 16-          |    |

|     | -             | Introduction                                                       | 16-          |    |

|     | 16.2          | Summary of Registers                                               | 16-          |    |

|     | 16.3          | Register Description                                               | 16-          |    |

| 17  |               | ry Subsystems                                                      | 17-          |    |

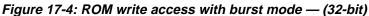

|     | 17.1          | ROM Interface                                                      | 17-          |    |

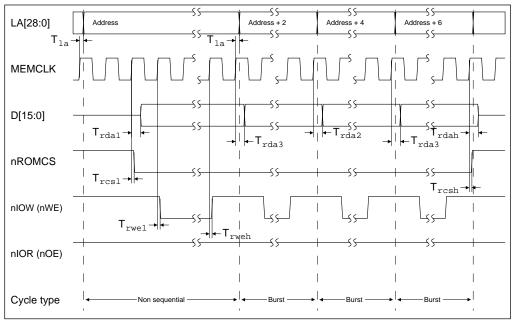

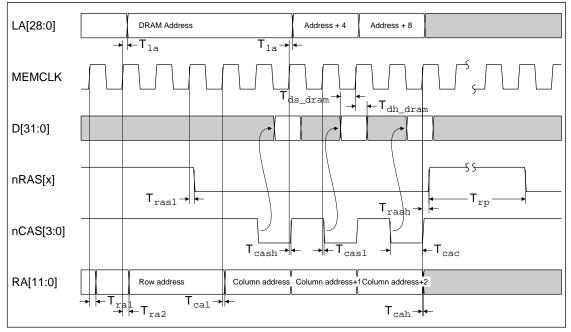

|     |               | DRAM Interface<br>DMA Channels                                     | -17<br>17-2  |    |

| 4.0 |               |                                                                    |              |    |

| 18  |               | bsystems                                                           | 18-          |    |

|     | 18.1          | Introduction                                                       | 18-          |    |

|     | 18.2<br>18.3  | I/O Address Space Usage<br>Additional I/O Chip Select Decode Logic | 18-<br>18-   |    |

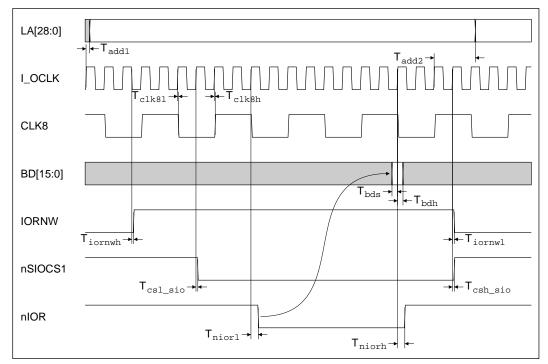

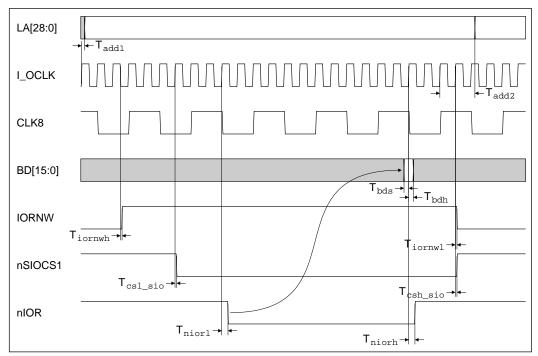

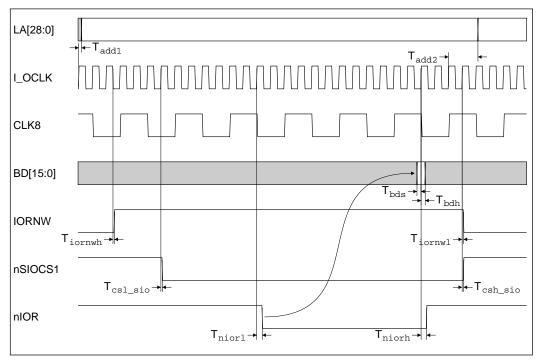

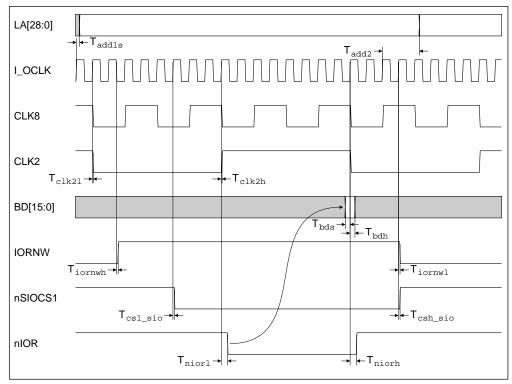

|     | 18.4          | Simple 8MHz I/O                                                    | 18-          |    |

|     |               | Module I/O                                                         | 18-1         |    |

|     | 18.6          | PC Bus-style I/O                                                   | 18-1         | 5  |

|     | 18.7          | DMA During I/O Cycles                                              | 18-2         |    |

|     | 18.8          | Clock Synchronization Conditions                                   | 18-2         |    |

|     | 18.9<br>18.10 | Keyboard/mouse Interface<br>Analog to Digital Converter Interface  | 18-3<br>18-3 |    |

|     | 18.11         | Timers                                                             | 18-3         |    |

|     | 18.12         | General-purpose, 8-bit-wide, I/O Port                              | 18-3         |    |

|     | 18.13         | ID and OD Open Drain I/O Pins                                      | 18-3         |    |

|     |               | Version and ID Registers                                           | 18-3         |    |

|     | 18.15         | Interrupt Control                                                  | 18-3         | 9  |

| 19  | Clocks        | s, Power Saving, and Reset                                         | 19-          | 1  |

|     | 19.1          | Clock Control                                                      | 19-          |    |

|     | 19.2          | Power Management                                                   | 19-          |    |

|     | 19.3          | Reset                                                              | 19-          | 6  |

| 20 | Bus Interface                                                                  | 20-1         |

|----|--------------------------------------------------------------------------------|--------------|

|    | 20.1 Bus Arbitration                                                           | 20-2         |

|    | 20.2 Bus Cycle Types<br>20.3 Video DMA Bandwidth                               | 20-2<br>20-3 |

|    | 20.4 Video DMA Latency                                                         | 20-4         |

| 21 | Memory Map                                                                     | 21-1         |

|    | 21.1 ARM7500FE Memory Map                                                      | 21-2         |

| 22 | DC and AC Parameters                                                           | 22-1         |

|    | 22.1 Absolute Maximum Ratings                                                  | 22-2         |

|    | <ul><li>22.2 DC Operating Conditions</li><li>22.3 DC Characteristics</li></ul> | 22-2<br>22-3 |

|    | 22.4 AC Parameters                                                             | 22-4         |

|    | 22.5 De-rating                                                                 | 22-6         |

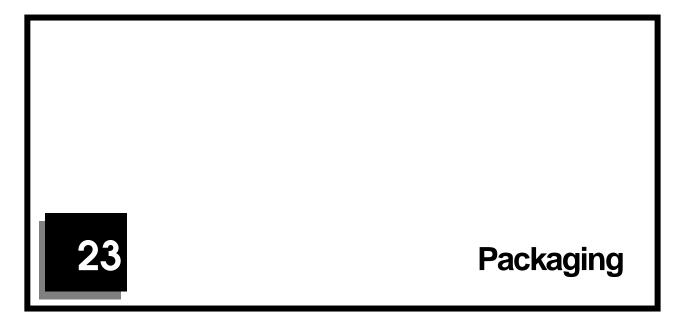

| 23 | Packaging                                                                      | 23-1         |

|    | 23.1 Pin Diagrams for the ARM7500FE                                            | 23-2         |

| 24 | Pinout                                                                         | 24-1         |

|    | 24.1 Pin Details                                                               | 24-2         |

| Α  | Initialization and Boot Sequence                                               | A-1          |

|    | A.1 Introduction<br>A.2 Sample Boot Sequence                                   | A-2<br>A-2   |

|    | A.3 Other Methods                                                              | A-2<br>A-3   |

| В  | Dual Panel Liquid Crystal Displays                                             | B-1          |

|    | B.1 Programming the Video Subsystem                                            | B-2          |

|    | B.2 Configuring DMA within ARM7500FE                                           | B-3          |

| •  | B.3 Cursor                                                                     | B-3          |

| С  | Using ASTCR at High MEMCLK Frequencies                                         | C-1          |

| _  | C.1 Using the ASTCR Register                                                   | C-2          |

| D  | Expanding PC-Style I/O to 32 Bit                                               | D-1          |

| _  | D.1 32-bit I/O                                                                 | D-2          |

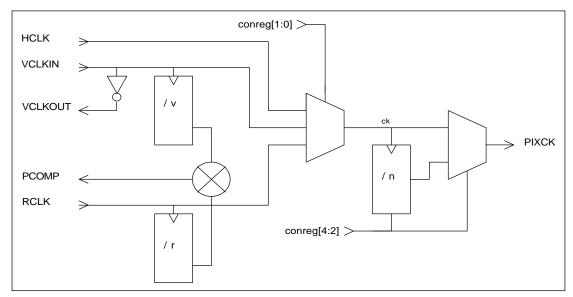

| Е  | ARM7500FE Video Clock Sources                                                  | E-1          |

|    | E.1 Introduction<br>E.2 Clock Sources                                          | E-2<br>E-2   |

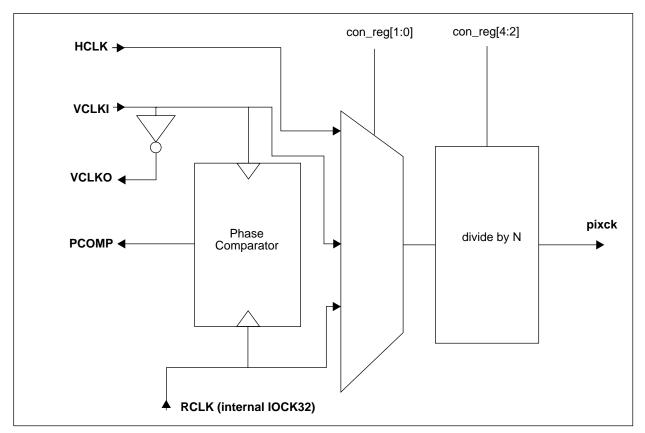

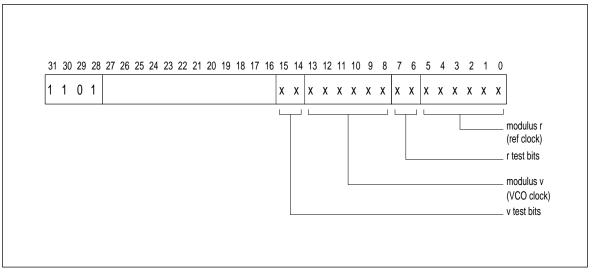

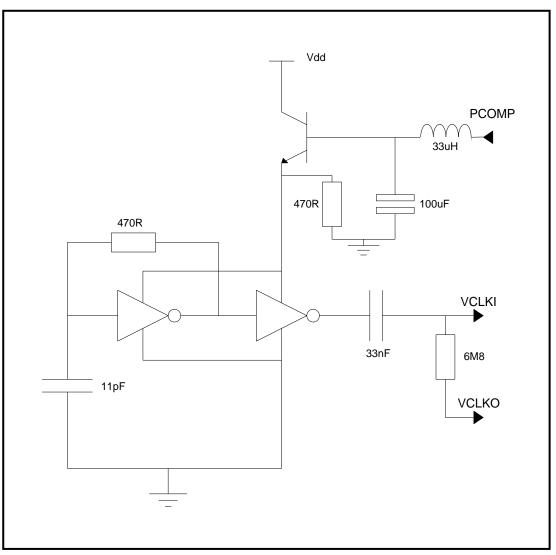

|    | E.3 Using the Phase Comparator                                                 | E-3          |

|    | E.4 Phase Comparator Reset                                                     | E-6          |

| F  | ARM7500FE Test Modes                                                           | F-1          |

|    | F.1 Introduction<br>F.2 Test Modes Description                                 | F-2          |

|    | F.2 Test Modes Description                                                     | F-2          |

ARM DDI 0077B

Contents-6

# **Open Access - Preliminary**

# Introduction

This chapter introduces the ARM7500FE single-chip microprocessor.

| 1.1  | Introduction                       | 1-2 |

|------|------------------------------------|-----|

| 1.2  | Functional Block Diagram           | 1-2 |

| 1.3  | ARM Processor Macrocell            | 1-2 |

| 1.4  | FPA Macrocell                      | 1-2 |

| 1.5  | Video and Sound Macrocell          | 1-4 |

| 1.6  | Clock Control and Power Management | 1-4 |

| 1.7  | Memory System                      | 1-5 |

| 1.8  | Other Features                     | 1-6 |

| 1.9  | Test Modes                         | 1-6 |

| 1.10 | Structure of ARM7500FE             | 1-7 |

| 1.11 | Resetting ARM7500FE Systems        | 1-7 |

### Introduction

#### 1.1 Introduction

ARM7500FE is a high-performance, low-power RISC-based single-chip computer centered around the ARM microprocessor core. To maximize the potential of the ARM processor macrocell, ARM7500FE contains memory and I/O control on-chip, enabling the direct connection of external memory devices and peripherals with the minimum of external components. A floating-point accelerator (FPA) is also integrated, resulting in outstanding maths performance.

ARM7500FE includes features which also make it particularly suitable for low-power portable applications. Both 32 and 16-bit wide memory systems are supported, allowing a lower-cost 16-bit-based system to be designed. The ARM7500FE will drive color CRT or color LCD panels. Monochrome single or dual panel LCDs with 16 levels of greyscaling can also be driven. Power-management circuitry is included with two power-saving states. The high level of integration achieved allows significant PCB area saving, and results in a very cost-competitive system.

ARM7500FE is also particularly suited to any application requiring high-quality video, sound and general I/O requirements, such as multimedia. The video controller provides up to 16 million colors from a 256-entry palette, running at up to 120MHz pixel clock rate. The sound subsystem includes a serial sound interface for CD quality 32-bit sound. Four on-chip A to D converters allow the connection of analog joysticks or similar control devices. The clocking scheme is very flexible, allowing either a very cheap system to be built using a single oscillator, or separate asynchronous clocks to be used for the CPU, memory and I/O subsystems, which gives an extremely flexible system, able to take advantage of the fastest available DRAM memory.

The wide range of features incorporated into ARM7500FE make it an extremely flexible device, which can be programmed according to the required application to optimise for high performance or low power, or a combination of both.

#### 1.2 Functional Block Diagram

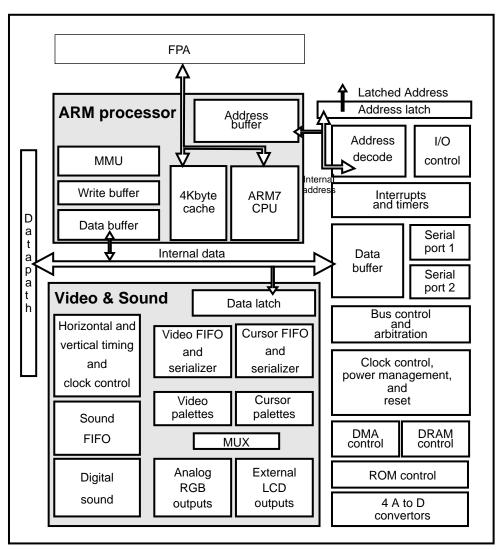

*Figure 1-1: Block diagram of the ARM7500FE* on page 1-3 gives a more detailed view of the functionality of the ARM7500FE single-chip computer.

#### 1.3 ARM Processor Macrocell

The ARM processor contains an ARM7 core with MMU, 4K cache, and write buffer.

#### 1.4 FPA Macrocell

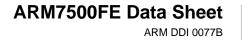

The FPA is a fully IEEE-754 compliant floating-point accelerator, and supports single, double and extended precision formats. It is connected to the ARM via the coprocessor interface and provides the same floating-point functionality as the FPA11.

Concurrent load/store and arithmetic units, and speculative execution are employed to give good floating-point performance.

# Open Access - Preliminary

Figure 1-1: Block diagram of the ARM7500FE

### Introduction

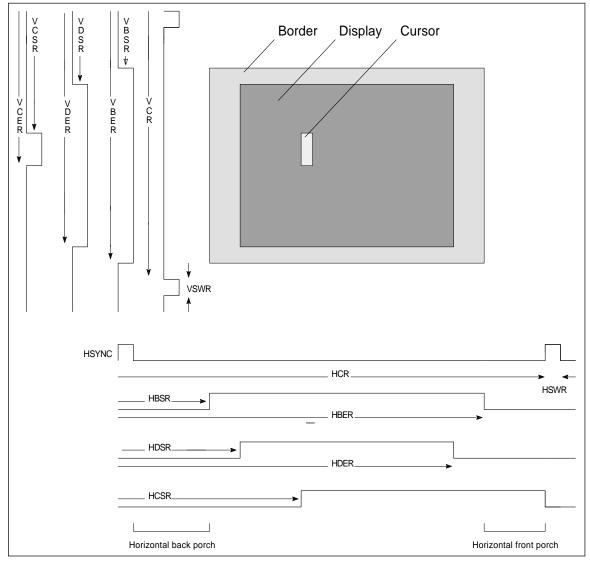

#### 1.5 Video and Sound Macrocell

The video and sound macrocell gives the ARM7500FE the flexibility to drive high specification CRT or low power LCD displays, and features the following:

- up to 120MHz pixel clock rate

- resolutions of up to 1024 x 768 pixels are directly supported (greater if external serialization is used)

- fully programmable display parameters

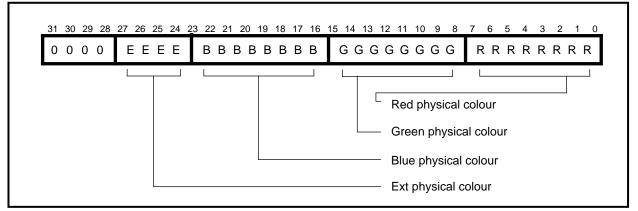

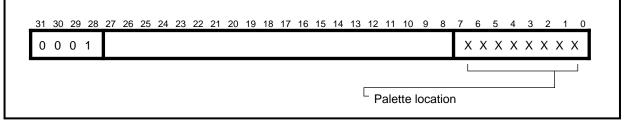

- 256-entry by 28 bit video palette

- red, green and blue 8-bit linear DACs to drive CRT

- 1,2,4,8,16,32 bits/pixel CRT modes

- up to 16 million colors

- external bits in palette for supremacy, fading, Hi\_Res

- single or dual panel LCD driving

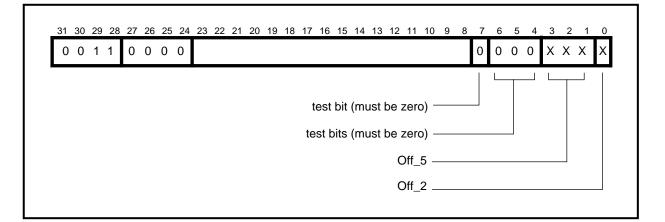

- 16-level grey scaler for LCD

- power-management features

- hardware cursor for all display modes

- sound system serial CD digital output

#### 1.6 Clock Control and Power Management

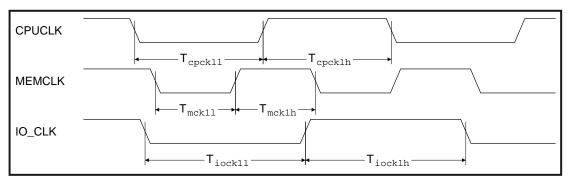

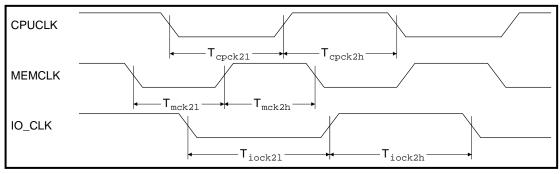

The clocking strategy for ARM7500FE has been designed for maximum flexibility, and includes separate clock inputs for the:

- CPU core clock

- Memory system clock

- I/O system clock (in addition to the video clock inputs).

Each of the three clock inputs has a selectable divide-by-two prescaler to generate an internal 50/50 mark-space ratio if required. Throughout this datasheet, all timing diagrams assume that **CPUCLK**, **MEMCLK**, and **I\_OCLK** are divided by one.

There are two levels of power management included.

- SUSPEND mode The clock to the CPU is stopped, but the display continues to work normally, ie. DMA unaffected.

- STOP mode All clocks are stopped. Two asynchronous wake-up event pins are provided to terminate stop mode. Circuitry is included on chip to stop external oscillators and restart them cleanly when required.

#### 1.7 Memory System

The memory system interface control logic is completely asynchronous in operation to the I/O control logic. This means that the clock to the memory controller can be increased in frequency to allow faster memory to be used. This implementation gives maximum system flexibility.

ARM7500FE can control a 32 or 16-bit wide memory system. The width of each bank of ROM or DRAM is selectable by programming appropriate register bits. Fast Page Mode or EDO DRAM types are supported.

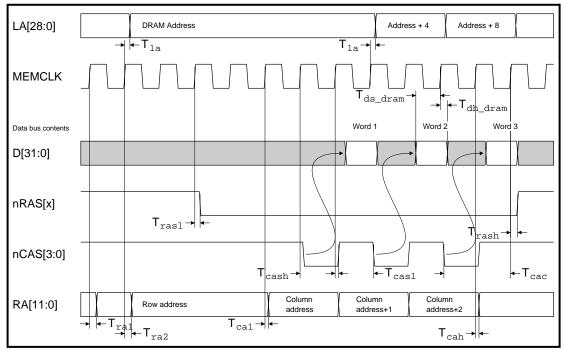

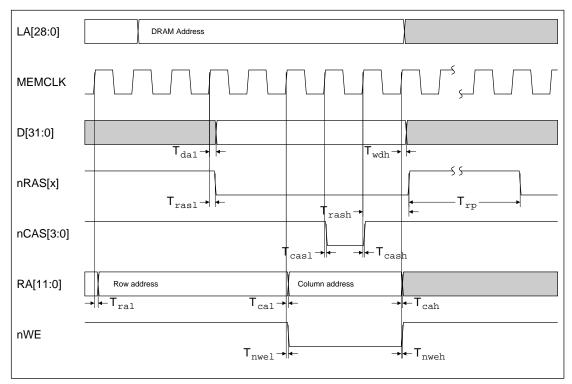

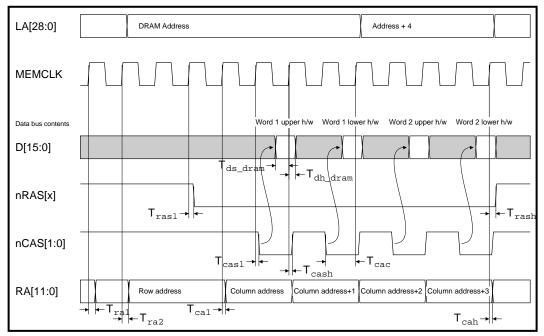

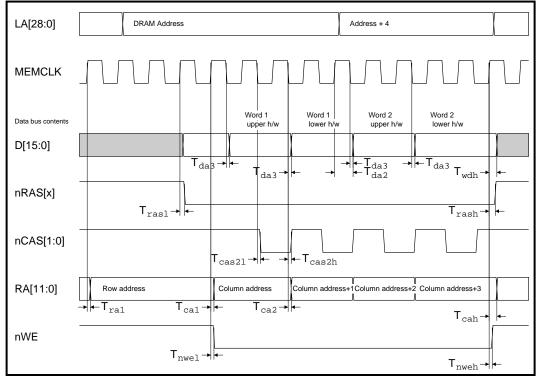

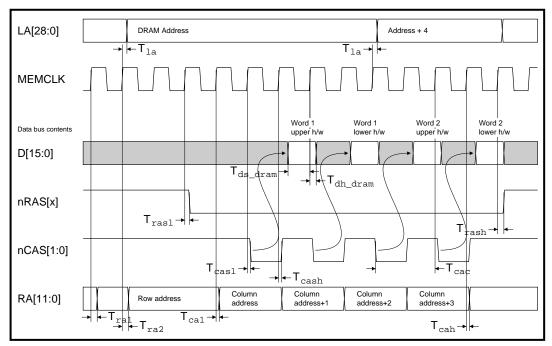

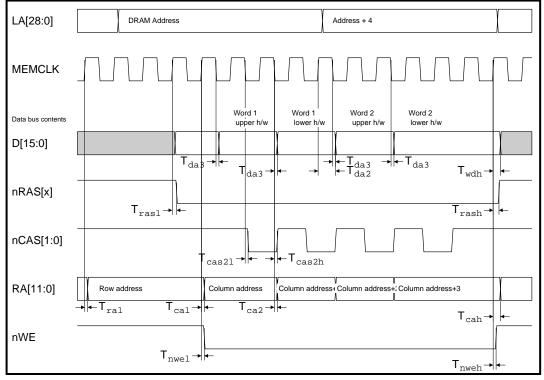

A DRAM controller is included which can directly drive up to 4 banks of DRAM. Four **nRAS** strobes individually select one of the four banks, and four **nCAS** strobes provide individual byte selection. The DRAM address multiplexing option provided allows a wide variety of DRAM sizes from 256K to beyond 16MB to be used. Up to 256 page mode transfers may occur in one sequential burst. When configured for operation with a 16-bit DRAM system, the DRAM controller will convert the access into two DRAM cycles to access the two halves of the 32-bit word. Byte transfers will only take one DRAM access cycle, even in 16-bit mode.

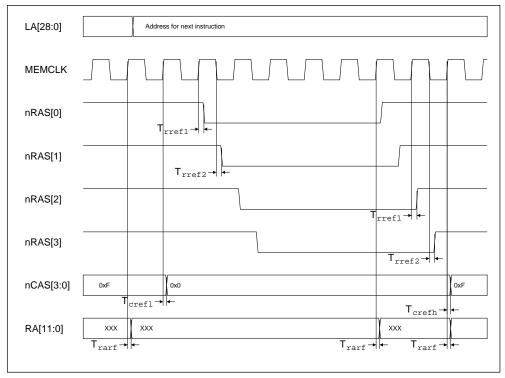

A programmable register allows one of four DRAM refresh rates to be selected. In addition, a register is provided to enable direct software control of the **nCAS** and **nRAS** lines for setting DRAM into a self-refresh state.

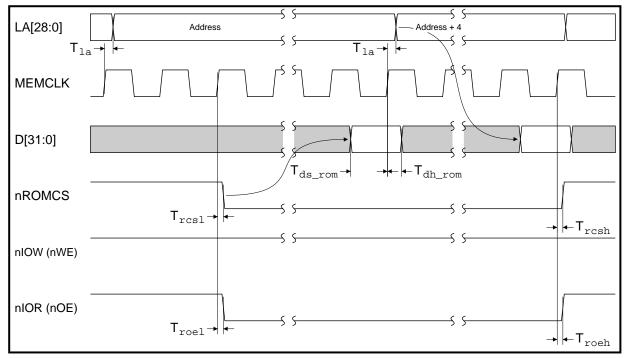

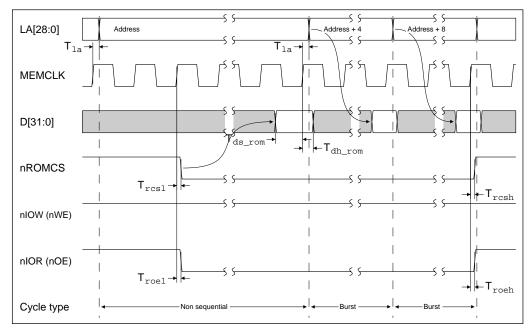

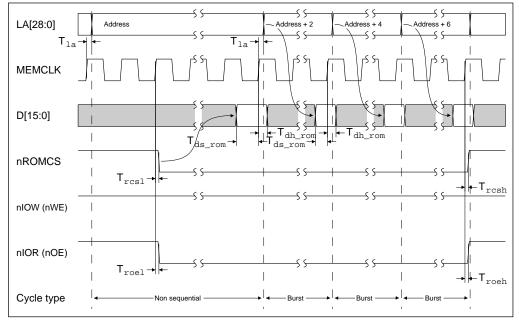

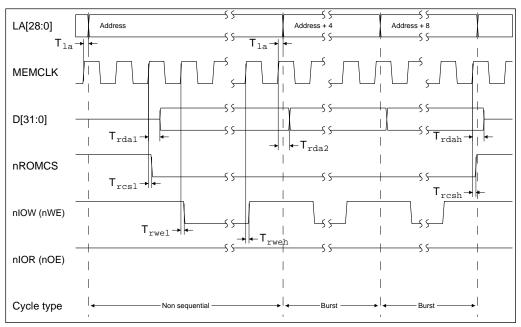

A ROM controller supports two 16MB banks of ROM with individually programmable read cycle timings. Support is provided for burst mode reads. Each ROM bank can be programmed to operate in 16-bit wide mode, and like the DRAM controller will convert accesses into two ROM cycles for the two halves of the 32-bit word. The ROM controller can be programmed to allow write cycles through this interface, allowing FLASH to be programmed, for example.

#### 1.7.1 DMA

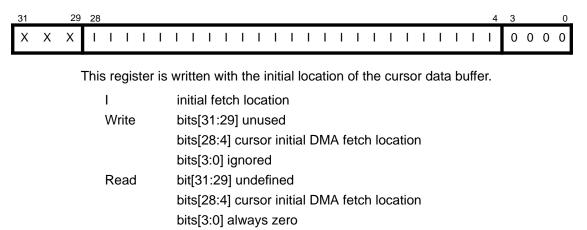

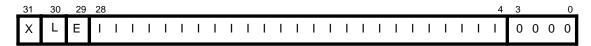

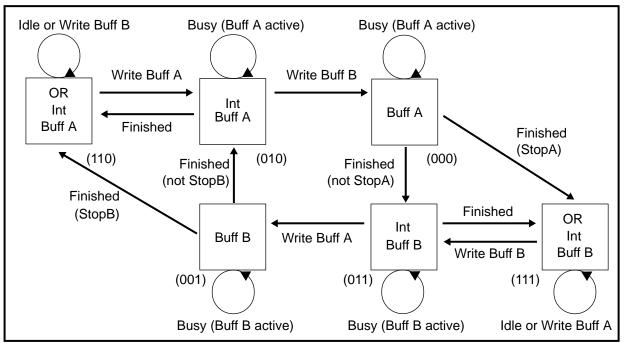

Three fully programmable DMA channels are included, for video, cursor and sound data. The DMA controller includes additional support for dual panel LCDs.

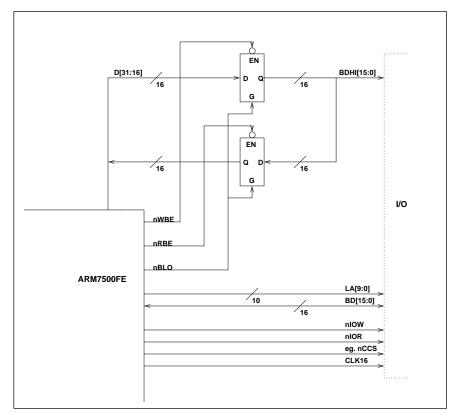

#### 1.7.2 I/O control

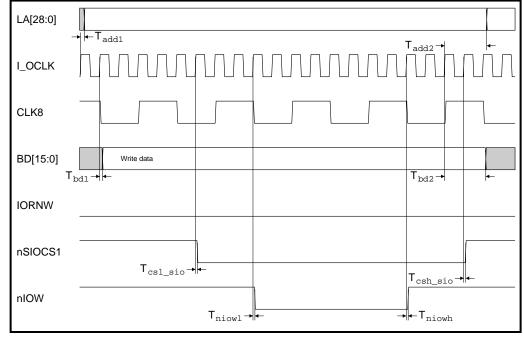

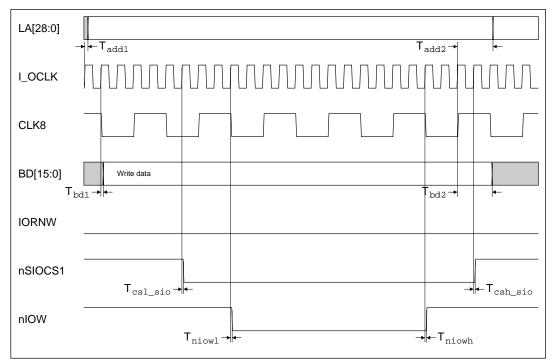

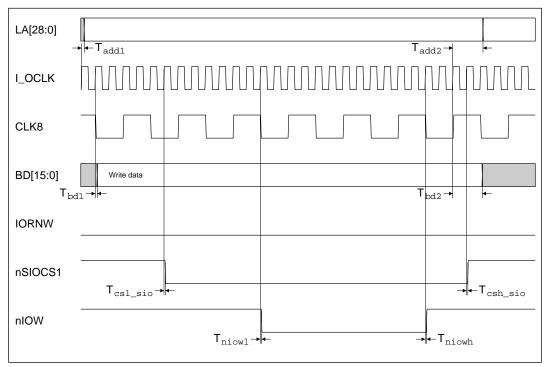

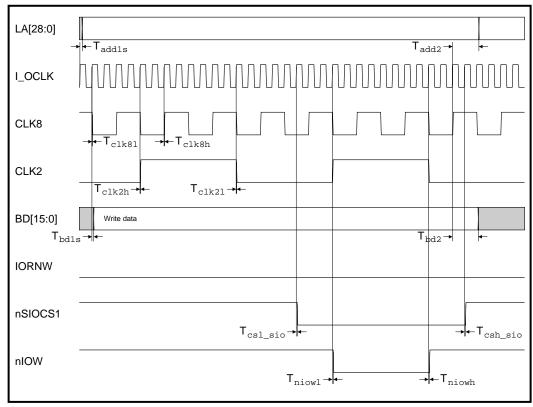

The I/O bus of ARM7500FE is 16-bits wide but for some types of access can be expanded to 32 bits by the use of external transceivers. The input clock I\_OCLK provides a reference for the I/O subsystem which is nominally 32MHz. The I/O features of this device can be separated into 3 distinct cycle types:

- Simple I/O with fixed 8MHz timings

- Module I/O with variable length 8MHz timings

- PC bus style I/O with fixed 16MHz timings and support for 32-bit data

#### Simple I/O

The Simple I/O type of access is 16-bit only and has a selection of 4 different cycle speeds selectable by address. When writing, the upper half-word of the ARM data bus is written out on the I/O bus. When reading, the I/O bus data is read back onto the lower half-word of the ARM data bus. During these accesses, a chip select is asserted with the appropriate **nIOR/nIOW** read or write strobe, based on the 8MHz clock **CLK8**.

### ARM7500FE Data Sheet

ARM DDI 0077B

### Introduction

#### Module I/O

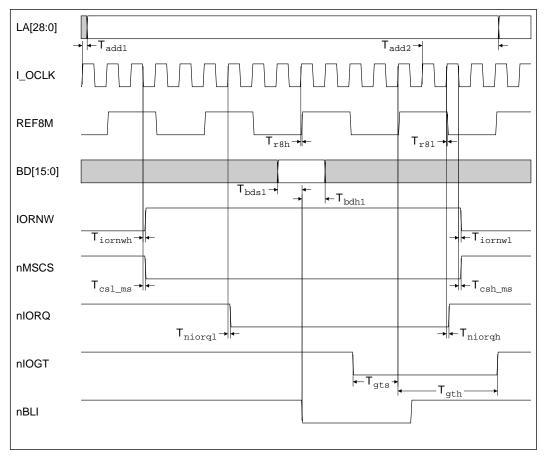

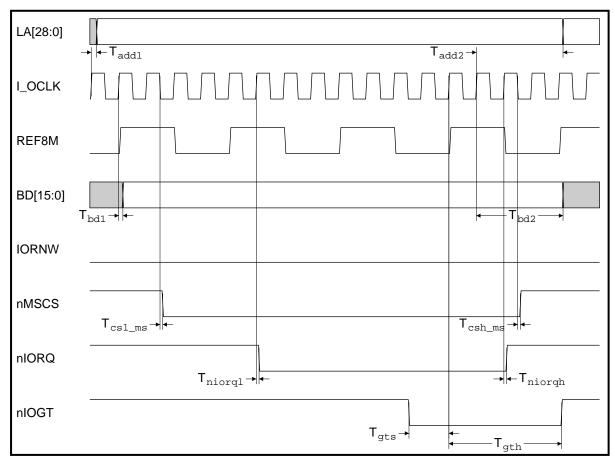

The Module I/O type of access is 16 bit only and its timing is controlled by a handshake mechanism with the external hardware. The signals **nIORQ** (output) and **nIOGT** (input) are used for this handshaking and are referenced to **REF8M**. When writing, the upper half-word of the ARM data bus is written out on the I/O bus. When reading, the I/O bus data is read back onto the lower half-word of the ARM data bus.

During these accesses, a chip select is asserted but the **nIOR/nIOW** read and write strobes are not used, although the **IORNW** signal is active.

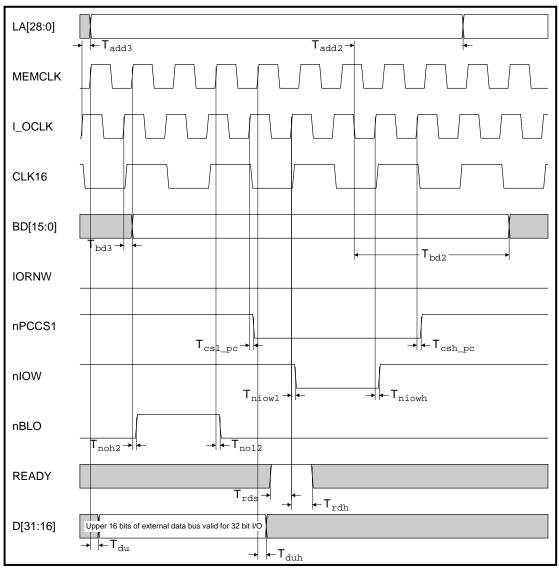

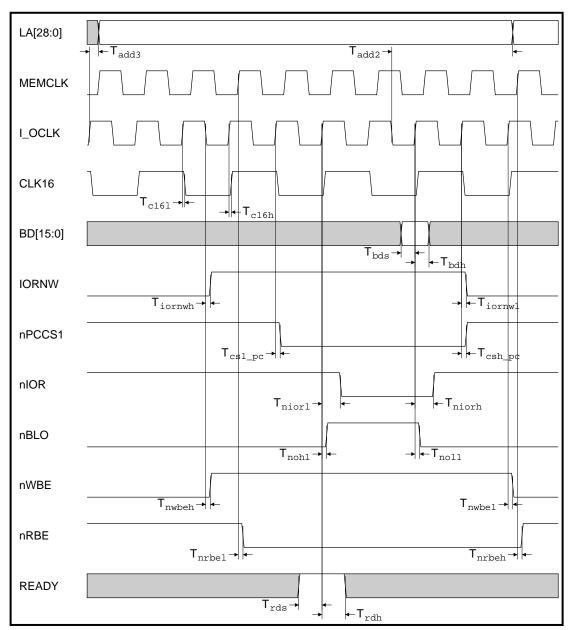

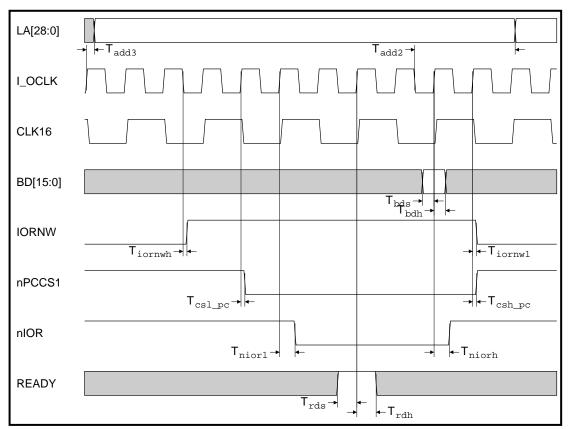

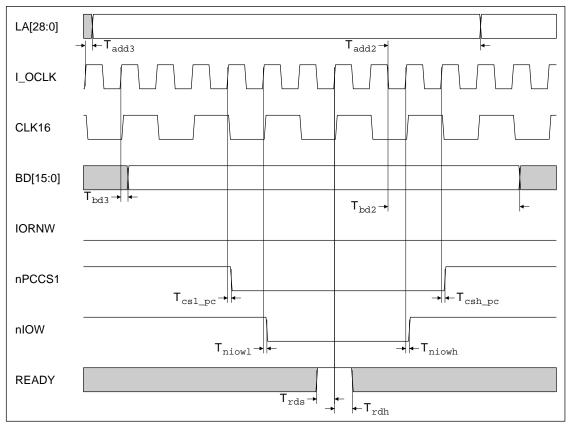

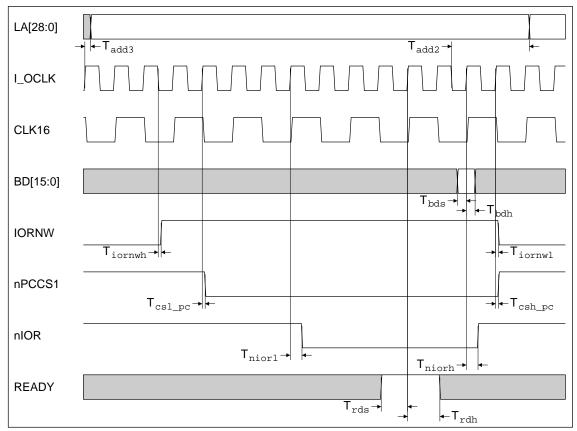

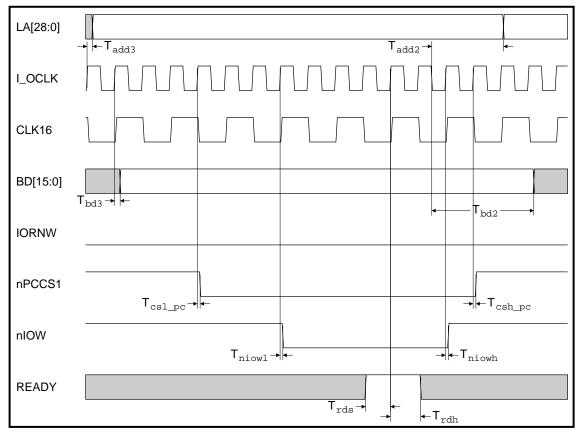

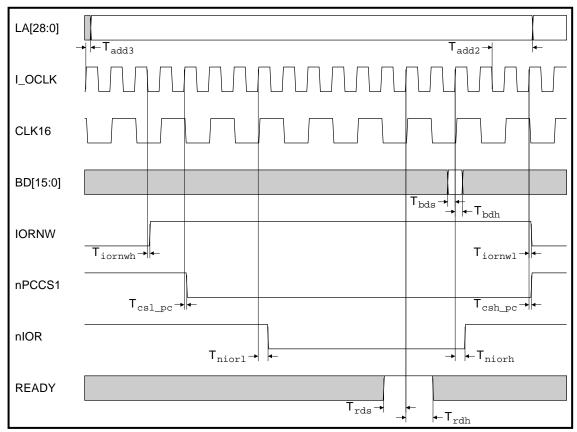

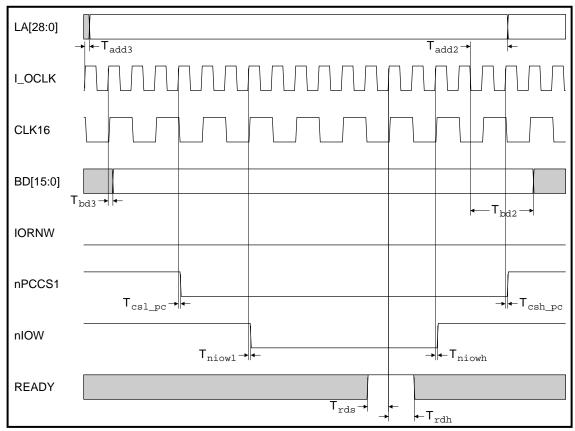

#### PC bus style I/O

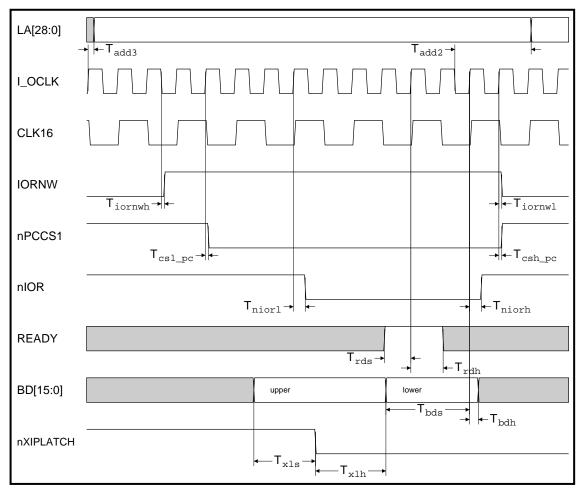

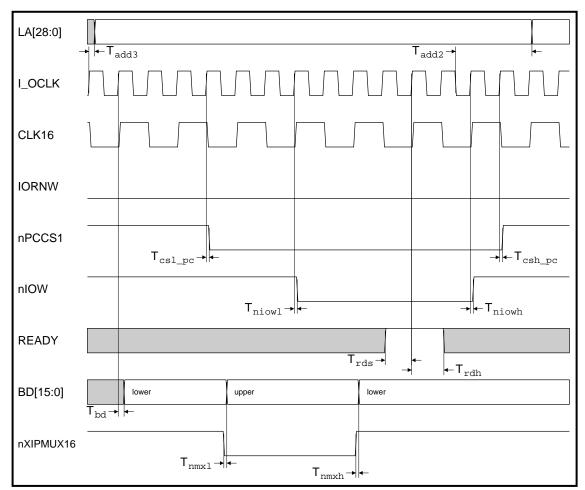

The PC bus style I/O type of access routes the lower half-word of the ARM bus through the device providing a direct 16-bit interface. Signals are generated to support the addition of external latches/drivers to extend the I/O data by 16 bits. The upper half-word of the ARM data bus is routed through these external devices if present.

There are 5 different address areas generating 5 different chip selects using the same type of access. There are 4 fixed cycle types based on the 16MHz clock, although the largest area only supports two of these cycle types. Any access may be held up by external circuitry removing the **READY** signal before the end of the cycle.

During these accesses, the relevant chip select is asserted as well as read or write strobes as appropriate.

Two special inputs are provided to allow external circuitry to route the full 32 bits through the 16-bit I/O bus using multiplexing. This would allow, for example, the execution of code from a 16-bit PCMCIA card with suitable external controller. On a read I/O, if this latching signal is used, the data read back onto the ARM data bus comes from the I/O bus instead of the external extension latches.

#### 1.8 Other Features

ARM7500FE includes four analog comparators, which can be used to create four A to D converter channels, and two serial keyboard/mouse ports.

There are 8 general-purpose open-drain I/O lines which can be used as inputs or open drain outputs and as interrupt sources if required.

An interrupt handler processes a variety of internal and external interrupt sources to generate the IRQ and FIQ interrupts for the ARM processor.

#### 1.9 Test Modes

ARM7500FE has an **nTEST** pin which is used to invoke various test modes. When **nTEST** is set LOW, the functionality of many of the pins will change depending on the values applied to the **nINT3**, **nINT6** and **nINT8** pins. The **nTEST** pin includes an on-chip pull-up, but it is recommended that the pin be pulled up to VDD externally too. See *Appendix F: ARM7500FE Test Modes*.

**Note:** The **nTEST** pin should never be forced LOW during normal operation.

#### 1.10 Structure of ARM7500FE

ARM7500FE includes three modified ARM macrocells:

- the ARM processor

- the FPA

- the video/sound macrocells

These macrocells are self-contained and the relevant control registers are contained within them. This has the effect that there are four sets of programmable registers within the ARM7500FE, which are accessed in different ways depending on their location.

#### 1.10.1 Register programming

The ARM processor register programming is described in *Chapter 4: The ARM Processor Programmers' Model*.

The FPA register programming is described in *Chapter 9: Floating-Point Coprocessor Programmer's Model*.

The video and sound macrocell's registers are programmed using only the internal ARM7500FE data bus (the address bus is not passed to the macrocell). The address 0x03400000 is decoded to provide a write strobe for the video macrocell registers, and the addressing of registers within the macrocell is decoded from the upper four or eight bits of the data word. This system is described more fully in *Chapter 12: The Video and Sound Programmer's Model*.

The remaining ARM7500FE registers, associated with Memory, I/O and general miscellaneous control, form a separate group and are programmed between addresses 0x03200000 and 0x032001F8. The majority of the registers are only eight bits wide, although all register addresses are word-aligned. These registers are described in *Chapter 16: Memory and I/O Programmers' Model*.

#### 1.10.2 Interaction between macrocells

Interaction between the macrocells occurs mainly across the ARM7500FE's internal 32-bit data bus, which is routed to the ARM and video/sound macrocells, and most of the other memory and I/O control logic. The ARM processor's address bus is routed to an internal address decoder where memory space is decoded to determine required cycle types and register addresses. The same address bus is latched and exported from the chip as the LA[28:0] bus. Only these 29 bits of the address bus are available externally.

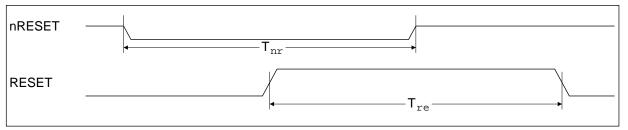

#### 1.11 Resetting ARM7500FE Systems

The ARM7500FE is designed to operate with both 16 and 32-bit wide ROM, which means that it must be capable of booting from either. To achieve this, the chip is always reset into 16-bit mode, which might be expected to cause difficulty when the chip is being booted up from 32-bit ROM. However, *Appendix A: Initialization and Boot Sequence* describes a simple code sequence which will allow the chip to be started up without difficulty under these circumstances.

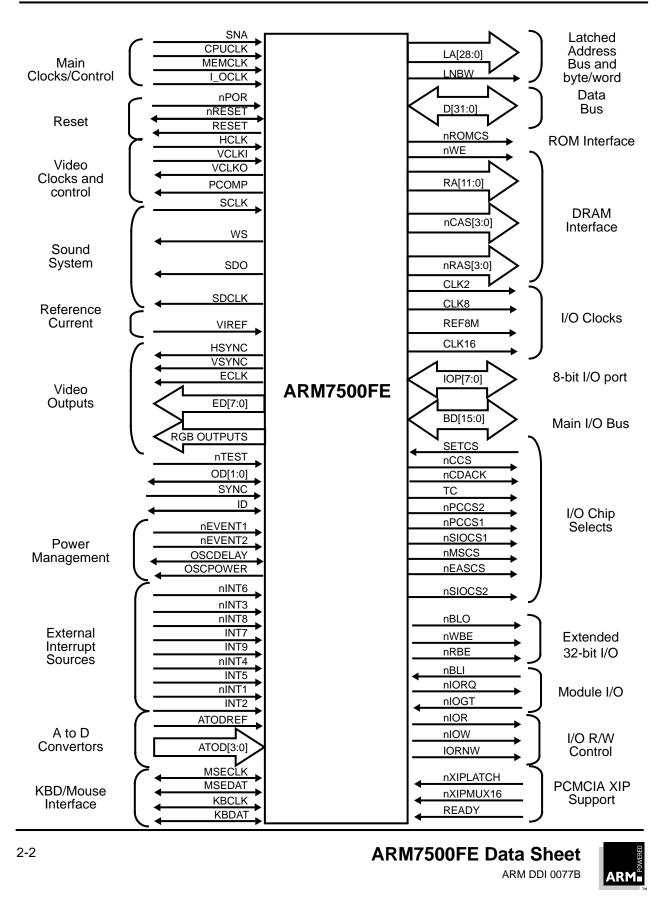

This chapter gives the name, type, and relevant details of each of the ARM7500FE signals.

2.1 Signal Description for ARM7500FE

#### 2.1 Signal Description for ARM7500FE

**Note:** When output signals are placed in the high impedance state for long periods, care must be taken to ensure that they do not float to an undefined logic level.

#### Key to signal types:

| IC   | Input, CMOS threshold                                         |

|------|---------------------------------------------------------------|

| OCZ  | Output, CMOS levels, tri-stateable                            |

| IT   | Input, TTL threshold                                          |

| ICS  | Input, CMOS Schmitt                                           |

| IA   | Input, analog                                                 |

| OA   | Output, analog                                                |

| BTZ  | Bidirectional, CMOS output, TTL threshold input level         |

| TOD  | Open drain, TTL input                                         |

| CSOD | Open drain, CMOS schmitt input                                |

| IAOD | Input, analog with programmable internal pull-down transistor |

|      |                                                               |

For outputs and bidirectionals, drive strength is classified 1,2 or 3. See *Chapter 22: DC and AC Parameters* for DC and AC characteristics.

Pin allocation is described in Chapter 24: Pinout .

| Name     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LA[28:0] | OCZ2 | Latched address bus. This bus is the latched version of the ARM address for memory accesses, changing on the falling edge of the internal MCLK signal.                                                                                                                                                                                                                                                                                                                                              |

| LNBW     | OCZ2 | Latched Not Byte word signal. This is a latched version of the internal NBW signal from the ARM processor, changing on the falling edge of the internal MCLK signal.                                                                                                                                                                                                                                                                                                                                |

| D[31:0]  | BTZ2 | The main data bus for the ARM7500FE. All external data transfers happen via this bus. When the ARM7500FE is configured for operation in 16-bit mode, only the lower 16 bits are used.                                                                                                                                                                                                                                                                                                               |

| SnA      | IC   | Synchronous/not Asynchronous. This pin is set according to the relationship required between the internal clock signals MCLK and FCLK for the ARM. If this pin is set HIGH, both the memory system and the CPU are driven from the <b>MEMCLK</b> pin, and the required synchronous timing relationship between the ARM processor clocks is generated automatically on-chip. If different clocks are to be used, for the <b>MEMCLK</b> and <b>CPUCLK</b> inputs, the <b>SnA</b> pin must be set LOW. |

| BOUT     | AO   | Blue Analog Output. The video signal analog outputs are designed to drive doubly-<br>terminated 75 lines.                                                                                                                                                                                                                                                                                                                                                                                           |

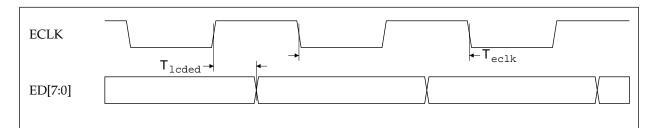

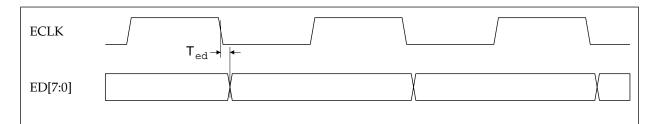

| ECLK     | OCZ3 | External Clock. When enabled, this clock validates the data on ED[7:0]. In normal video mode, it runs at the pixel rate, but when LCD data is being produced, it runs at a quarter of the pixel rate.                                                                                                                                                                                                                                                                                               |

Table 2-1: ARM7500FE signal description

| Name       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                    |  |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ED[7:0]    | OCZ2 | External Data. This is the digital video output port of the ARM7500FE. From this, the digital equivalent of the analog output may be produced in any color, or data from the external palette may be produced. This may be used for a variety of purposes such as fading or supremacy. Also, data for driving LCD panels is output from this port. Data produced is validated by <b>ECLK</b> . |  |

| GOUT       | AO   | Green Analog Output. The video signal analog outputs are designed to drive doubly-terminated $75\Omega$ lines.                                                                                                                                                                                                                                                                                 |  |

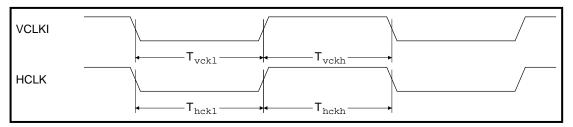

| HCLK       | ІТ   | High speed Clock for use with video subsystem.                                                                                                                                                                                                                                                                                                                                                 |  |

| HSYNC      | OCZ3 | Horizontal Synchronization. There are two synchronization outputs on ARM7500FE, <b>HSYNC</b> and <b>VSYNC</b> . Dependent on the state of bits 17 and 16 in the video External register, either a horizontal or a composite (NOR) sync may be output on this pin, in either polarity. The width of the <b>HSYNC</b> pulse is definable in units of 2 pixels.                                   |  |

| PCOMP      | OCZ1 | Phase Comparator Output for use with VCLK pins.                                                                                                                                                                                                                                                                                                                                                |  |

| ROUT       | AO   | Red Analog Output. The video signal analog outputs are designed to drive doubly-terminated 75 $\Omega$ lines.                                                                                                                                                                                                                                                                                  |  |

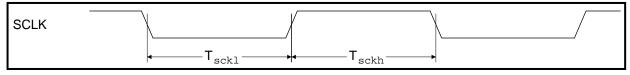

| SCLK       | IT   | Sound Clock. This signal can be used to clock the sound system, when a clock asynchronous to the internal video reference clock is required.                                                                                                                                                                                                                                                   |  |

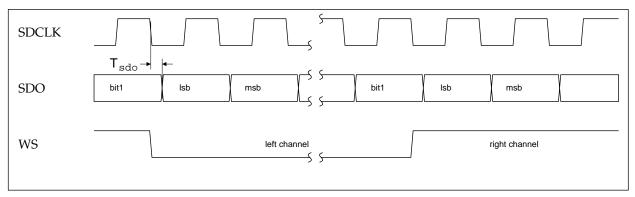

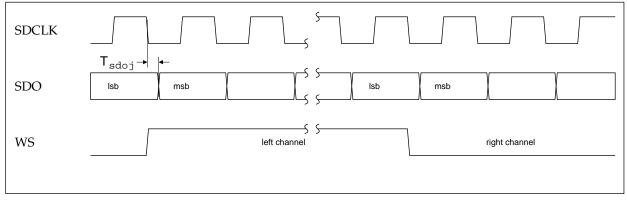

| SDCLK      | OCZ2 | Serial Data Clock. This clock validates serial sound data on its rising edge.                                                                                                                                                                                                                                                                                                                  |  |

| SDO        | OCZ2 | Serial Data Out. Serial sound data is output from this pin.                                                                                                                                                                                                                                                                                                                                    |  |

| SYNC       | IT   | External SYNC. This signal is used to synchronize ARM7500FE with another video system.                                                                                                                                                                                                                                                                                                         |  |

| VCLKI      | IC   | Phase Comparator Clock In (for video subsystem).                                                                                                                                                                                                                                                                                                                                               |  |

| VCLKO      | OCZ2 | Phase Comparator Clock Out (for video subsystem).                                                                                                                                                                                                                                                                                                                                              |  |

| VDD_Analog |      | Positive (+5V) supply for analog video system.                                                                                                                                                                                                                                                                                                                                                 |  |

| VIREF      | IA   | Video Reference Current. The video DACs need a reference current in order to calibrate them. A constant current source is recommended, although a resistor up to <b>VDD</b> is sufficient for many applications. This current also generates the constant source for the A to D comparators.                                                                                                   |  |

| VSS_Analog |      | Supply ground for analog video system.                                                                                                                                                                                                                                                                                                                                                         |  |

| VSYNC      | OCZ3 | Vertical Synchronization. Dependent on the state of bits 19 and 18 in the external register, either a vertical or a composite (XNOR) sync may be output on this pin, in either polarity. The width of the <b>VSYNC</b> pulse may be defined in units of a raster.                                                                                                                              |  |

| ws         | OCZ2 | Word Select. This signal denotes whether the output serial data is for the left hand stereo channel or the right hand channel.                                                                                                                                                                                                                                                                 |  |

Table 2-1: ARM7500FE signal description (Continued)

#### ARM7500FE Data Sheet ARM DDI 0077B

| Name      | Туре  | Description                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| nTEST     | IT    | Test mode input. This pin should be held permanently HIGH.<br>It is only intended to be used during production test of the ARM7500FE. An on-chip<br>pull-up is included, but it is advisable to fit an external pull-up resistor to this pin.                   |  |  |  |  |  |

| nWE       | OCZ3  | Write enable. Active low.                                                                                                                                                                                                                                       |  |  |  |  |  |

| RA[11:0]  | OCZ2  | DRAM row/column multiplexed address bus. Addresses for this bus are decoded from the ARM processor address for normal memory accesses, and are generated by the DMA controller for DMA.                                                                         |  |  |  |  |  |

| nRAS[3:0] | OCZ3  | DRAM row address strobes. Each of these selects one of the four banks of DRAM available.                                                                                                                                                                        |  |  |  |  |  |

| nCAS[3:0] | OCZ2  | DRAM column address strobes. These select the byte within the word for DRAM accesses.                                                                                                                                                                           |  |  |  |  |  |

| VDD_ATOD  | power | Positive 5V supply for the A to D converter comparators                                                                                                                                                                                                         |  |  |  |  |  |

| VSS_ATOD  | power | Analog ground for the A to D converter comparators                                                                                                                                                                                                              |  |  |  |  |  |

| ATOD[3:0] | IAOD  | Four A to D channel input voltages.                                                                                                                                                                                                                             |  |  |  |  |  |

| ATODREF   | IA    | Reference voltage for the A to D converter comparators.                                                                                                                                                                                                         |  |  |  |  |  |

| OSCPOWER  | OCZ1  | Enable signal for the system oscillator(s). When LOW, this signal can be used to disable the external oscillator(s).                                                                                                                                            |  |  |  |  |  |

| OSCDELAY  | CSOD1 | Requires an RC network to generate a fixed delay when restarting the system oscillator(s) on exit from STOP mode.                                                                                                                                               |  |  |  |  |  |

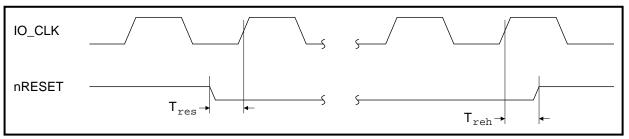

| RESET     | OCZ1  | Reset output, synchronized version of internal system reset signal.                                                                                                                                                                                             |  |  |  |  |  |

| nRESET    | CSOD2 | Open drain output and 'soft' reset input. This pin is sampled every 1 $\mu$ s for reset events, so to guarantee a successful reset, a reset pulse applied to this pin must be longer than 1 $\mu$ s. (Note-1 $\mu$ s, assuming the internal I/O clock is 32MHz) |  |  |  |  |  |

| nROMCS    | OCZ1  | ROM Chip select. Goes LOW to indicate a ROM access.                                                                                                                                                                                                             |  |  |  |  |  |

| I_OCLK    | IC    | I/O system clock. This clock input should always be 32MHz when in divide by 1 mode, and 64MHz in divide by 2 mode.                                                                                                                                              |  |  |  |  |  |

| MEMCLK    | IC    | Memory system clock. In synchronous mode, ARM processor FCLK is also driven from this clock.                                                                                                                                                                    |  |  |  |  |  |

| CPUCLK    | IC    | Clock used to create FCLK for the ARM CPU in asynchronous mode. When SnA is HIGH this should be tied HIGH or LOW permanently.                                                                                                                                   |  |  |  |  |  |

| BD[15:0]  | BTZ2  | The main external 16-bit I/O bus.                                                                                                                                                                                                                               |  |  |  |  |  |

| MSCLK     | TOD2  | Mouse clock. An open drain pin for the mouse PS/2 interface.                                                                                                                                                                                                    |  |  |  |  |  |

| MSDATA    | TOD2  | Mouse data. An open drain pin for the mouse PS/2 interface.                                                                                                                                                                                                     |  |  |  |  |  |

| KBCLK     | TOD2  | Keyboard clock. An open drain pin for the keyboard PS/2 interface.                                                                                                                                                                                              |  |  |  |  |  |

Table 2-1: ARM7500FE signal description (Continued)

ARM7500FE Data Sheet

**Open Access - Preliminary**

| Name     | Туре | Description                                                                                                                                                                                            |  |  |  |  |  |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| KBDATA   | TOD2 | Keyboard data. An open drain pin for the keyboard PS/2 interface.                                                                                                                                      |  |  |  |  |  |

| nPOR     | ICS  | Power on reset. Any LOW transitions on this pin are detected and stretched to ensure full reset.                                                                                                       |  |  |  |  |  |

| IOP[7:0] | TOD1 | 8 bit wide I/O port. Each bit is directly controllable via an ARM7500FE register, and can be used as an interrupt source if required.                                                                  |  |  |  |  |  |

| ID       | TOD1 | The ID pin can be used to activate a system ID chip. It is forced LOW during the power on reset sequence.                                                                                              |  |  |  |  |  |

| OD[1:0]  | TOD1 | Two open drain pins which (unlike the <b>IOP[7:0]</b> bus) cannot be used to generate interrupts, but can be used as general purpose I/O pins, for example to communicate with a real time clock chip. |  |  |  |  |  |

| SETCS    | IC   | <b>SETCS</b> selects between two address decoding options for the three main I/O chip selects. It affects the outputs <b>nEASCS</b> , <b>nMSCS</b> and <b>nSIOCS2</b> .                                |  |  |  |  |  |

| nINT1    | IT   | Falling edge triggered interrupt pin. This pin also has the feature that its value can be read directly in the IOCR I/O control register.                                                              |  |  |  |  |  |

| INT2     | IT   | Rising edge triggered interrupt pin. Can generate an IRQ interrupt.                                                                                                                                    |  |  |  |  |  |

| nINT3    | IT   | Active LOW interrupt pin. Can generate an IRQ interrupt.                                                                                                                                               |  |  |  |  |  |

| nINT4    | IT   | Active LOW interrupt pin. Can generate an IRQ interrupt.                                                                                                                                               |  |  |  |  |  |

| INT5     | IT   | Active HIGH interrupt pin. Can be used to generate either an IRQ or a FIQ interrudepending on the status of the relevant mask register bits.                                                           |  |  |  |  |  |

| nINT6    | IT   | Active LOW interrupt pin. Can generate either an IRQ or a FIQ depending on the programming of the mask registers.                                                                                      |  |  |  |  |  |

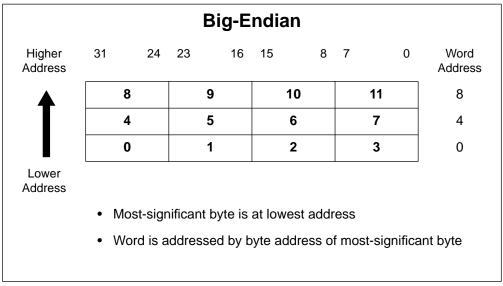

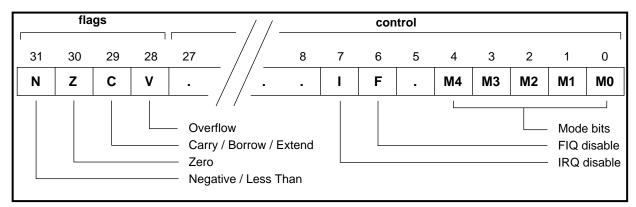

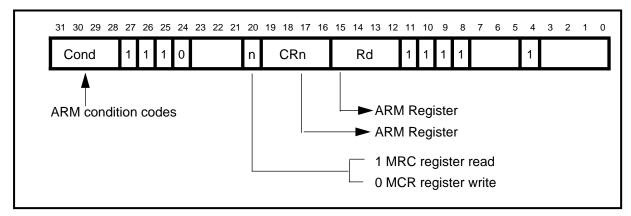

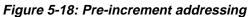

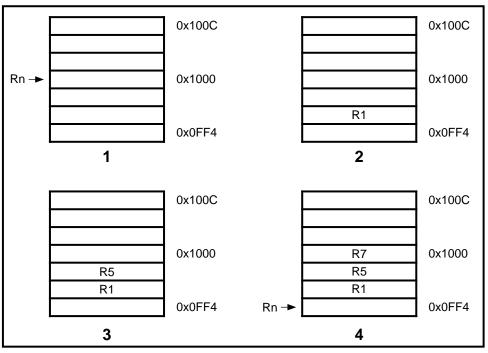

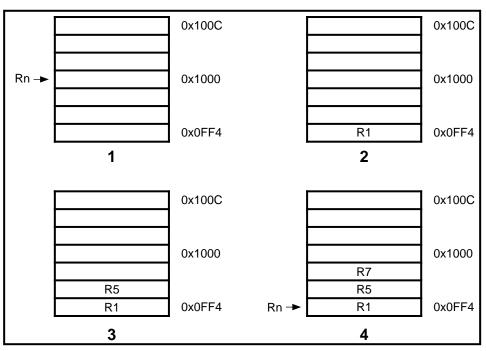

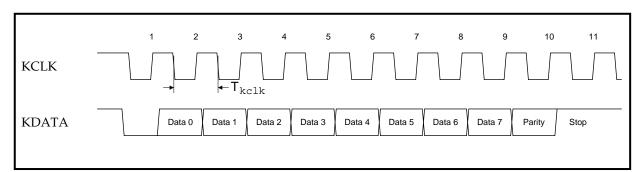

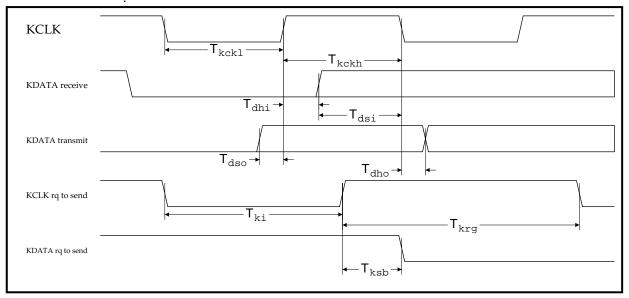

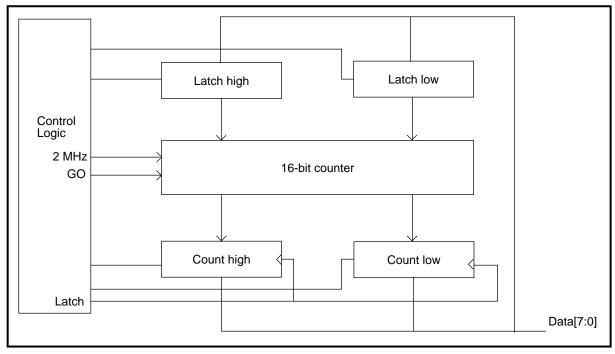

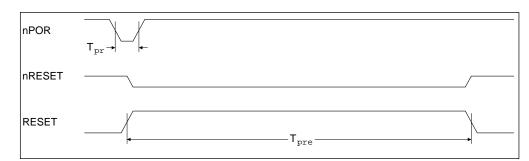

| INT7     | IT   | Active HIGH interrupt pin. Can generate an IRQ interrupt.                                                                                                                                              |  |  |  |  |  |